# **Manual ADQ14**

This manual describes how to get the full potential out of Teledyne SP Devices' digitizer ADQ14. The manual includes these steps:

- Set up the analog front-end

- Master the triggers

- Control the acquisition

- Manage the sampling clock

- Understanding data transfer to host PC

- Using GPIO

# **Table of content**

| 1     | INTRODUCTION                                                         | . 5 |

|-------|----------------------------------------------------------------------|-----|

| 1.1   | ADQ14 Architecture                                                   | . 5 |

| 1.2   | Fundamental design properties                                        | . 5 |

| 1.2.1 | Data format                                                          |     |

| 1.2.2 | Calibration                                                          |     |

|       | Data acquisition nomenclature                                        |     |

|       | ADQ14 sampling clock frequency                                       |     |

|       | System clocks                                                        |     |

|       | Analog signal range                                                  |     |

| 1.2.0 |                                                                      |     |

| 2     | SETTING UP THE ANALOG FRONT-END                                      | . 9 |

| 2.1   | ADQ14 AFE block diagram                                              | . 9 |

| 2.2   | Set analog DC-offset                                                 | 10  |

| 2.3   | Adjusting the digital gain and offset                                | 10  |

|       |                                                                      |     |

| 3     | SIGNAL QUALITY ENHANCEMENT                                           | 11  |

| 3.1   | Digital Baseline Stabilizer                                          | 11  |

| 3.2   | Interleaving correction ADX                                          | 11  |

|       | •                                                                    |     |

| 4     | TRIGGER                                                              |     |

| 4.1   | Trigger block diagram                                                |     |

| 4.2   | Position of the trigger in the data                                  | 13  |

| 4.3   | Timestamp                                                            | 13  |

| 4.3.1 | Timestamp definitions                                                | 13  |

| 4.3.2 | Timestamp reset                                                      | 14  |

| 4.4   | Blocking triggers for synchronization                                |     |

| 4.4.1 | Function overview                                                    |     |

| 4.4.2 | Block triggers once                                                  |     |

|       | Windowing triggers                                                   |     |

|       | Gating and windowing triggers                                        |     |

|       | Programming sequence for using trigger blocking                      |     |

| 4.5   | Trigger jitter                                                       |     |

|       | Trigger jitter definitions                                           |     |

|       | Asynchronous triggering                                              |     |

|       | Synchronous trigger                                                  |     |

|       | Extended trigger resolution                                          |     |

| 4.6   | Software trigger                                                     |     |

|       |                                                                      |     |

|       |                                                                      | 20  |

|       | External trigger TRIG front panel connector                          |     |

|       | External trigger SYNC connector                                      |     |

|       | Driving the external TRIG/SYNC signal by controlling input impedance |     |

| 4.8   | External trigger in the backplane                                    |     |

|       | PXIe interface                                                       |     |

|       | MTCA.4 interface                                                     |     |

| 4.9   | Level trigger                                                        |     |

|       | Setting the level trigger level                                      |     |

|       | Level trigger and DBS                                                |     |

| 4.9.3 | Controlling noise sensitivity                                        | 25  |

|       | Internal trigger                                                     |     |

|       | Trigger output                                                       |     |

|       | Trigger output port selection                                        |     |

|       | Prame sync output on SYNC connector                                  |     |

|       | · · · · · · · · · · · · · · · · · · ·                                |     |

| 4.11.4       | 3Trigger event indicator                                            | . 27 |

|--------------|---------------------------------------------------------------------|------|

| 4.11.5       | 5Distributing level trigger                                         | . 29 |

| 5            | CLOCK                                                               | 30   |

| 5.1          | Clock domains                                                       | 30   |

| 5.2          | Flexible clock network                                              | 30   |

| 5.3          | Front panel SMA connector                                           | 31   |

| 5.4          | Internal clock reference                                            | 31   |

| 5.5          | External clock reference                                            | 31   |

| 5.6          | Internal clock generator                                            | 32   |

| 5.7          | External clock                                                      |      |

| 5.8          | Clock reference output                                              |      |

| 5.9          | Sample skip                                                         |      |

|              | ·                                                                   |      |

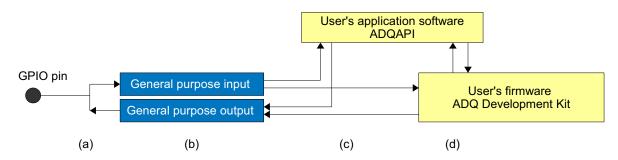

| 6            | GPIO                                                                |      |

| 6.1          | GPIO with TRIG and SYNC                                             |      |

| 6.2          | Using GPIO as a trigger                                             |      |

| 6.3          | Output                                                              |      |

| 6.4          | GPIO in ADQ Development Kit                                         |      |

| 6.5          | ADQ14–PCIe SYNC connectors                                          |      |

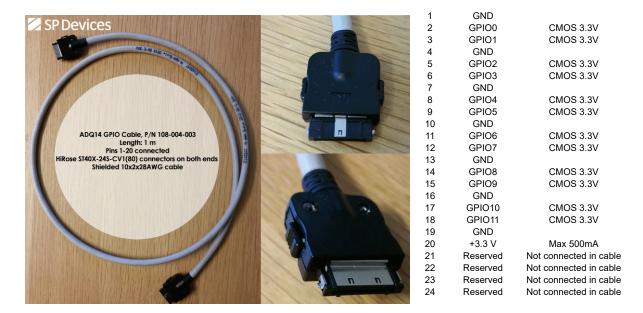

| 6.6          | Dedicated GPIO connector available with options –GPIO, –VG or –MTCA |      |

| 6.7          | ADQ14 Custom GPIO expansion                                         | 36   |

| 7            | ACQUISITION CONTROL                                                 | 37   |

| 7.1          | Multi-thread notice                                                 |      |

| 7.2          | Acquisition memory                                                  |      |

| 7.3          | Acquisition modes                                                   |      |

|              | Continuous streaming acquisition                                    |      |

|              | Triggered streaming acquisition                                     |      |

|              | Multi-record acquisition                                            |      |

| 7.4          | Data transfer modes                                                 |      |

| 7.4.1        | Streaming data transfer mode                                        |      |

|              | User-scheduled data transfer mode                                   |      |

|              | Transfer buffers                                                    |      |

| 7.4.4        | User's buffers                                                      | . 44 |

| 7.5          | Users application software consuming data                           | 44   |

| 7.6          | Record header                                                       | 45   |

| 7.6.1        | Metadata                                                            | . 45 |

|              | Record Status                                                       |      |

|              | User ID                                                             |      |

|              | Serial number                                                       |      |

|              | Channel                                                             |      |

|              | Record number                                                       |      |

|              | Data format                                                         |      |

| 7.6.8<br>7.7 | Record length  Over-range and under-range                           |      |

| 1.1          |                                                                     |      |

| 8            | HOST PC CONNECTION                                                  | 48   |

| 8.1          | USB interface                                                       | 48   |

| 8.2          | PCI Express interface                                               | 48   |

| 8.3          | Using several units                                                 | 48   |

|              | Using several digitizers from a single application.                 |      |

| 8.3.2        | Using several digitizers from a several applications.               | . 48 |

### 1 INTRODUCTION

The purpose of this manual is to explain how the digitizer is operated. The datasheet [1] contain parameters for the specific versions of digitizer. References to software commands are made. In some places, pseudo code is used for description. See [2] for details on how to use the software commands and see [3] for general guidelines on programming the digitizer.

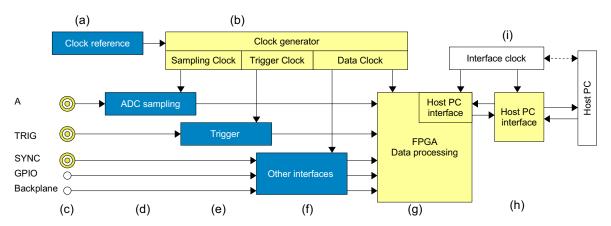

### 1.1 ADQ14 Architecture

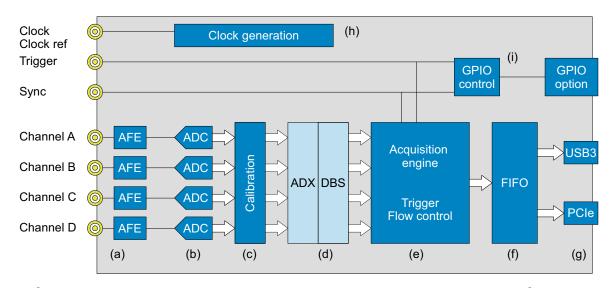

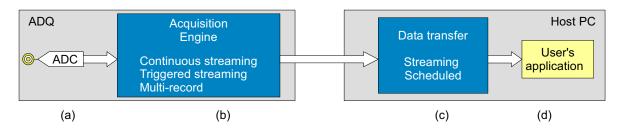

The ADQ14 architecture is given in **Figure 1**. References to the corresponding sections with further information are also included.

| # | DESCRIPTION                                                                                                                                                       | REFERENCE |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| а | Signal conditioning analog front-end.                                                                                                                             | 2         |

| b | High speed and high resolution A/D converter. The A/D converters operate at 500 MSPS, 1 GSPS or 2 GSPS depending on version of the ADQ14.                         | 3         |

| С | Calibration.                                                                                                                                                      | 2         |

| d | Teledyne SP Devices' proprietary technologies for signal quality enhancement; ADX for SFDR in radio systems and DBS for baseline stability in pulse data systems. | 3         |

| е | Acquisition engine that handles triggers and controls the data flow.                                                                                              | 4, 7      |

| f | Data FIFO to buffer data before transmission to the host PC.                                                                                                      | 7         |

| g | The data transfer to the host PC is through a PCle or a USB3.0 link.                                                                                              | 7         |

| h | Flexible clock generator.                                                                                                                                         | 5         |

| i | General Purpose digital Input and Output control.                                                                                                                 | 6         |

Figure 1: ADQ14 architecture.

# 1.2 Fundamental design properties

There are some fundamental design properties that are necessary to understand before continuing.

#### 1.2.1 Data format

The ADC components of ADQ14 has 14 bits resolution, while the data format inside the ADQ14 and out to the host PC is 16 bits. The 14 bits from the ADCs are MSB aligned in this 16 bit data word. Thus initially the 2 LSBs are zero.

The number representation is 2's complement. The full scale maximum code is then 32 767 and the full scale minimum code is –32 768. Overflow or underflow at any position in the signal path will saturate the data and turn on an overflow flag. See **Section 7.7** for more information on over- and under-flow.

The 2 LSBs may not be zero in the data output from the ADQ14. Calibration and other computations in the FPGA may result in fractional result. This is not rounded to 14 bits in order to avoid adding computational noise.

Example 1: A 14 bits sequence of data is subject to a gain calibration parameter of 1063. This means that the digital word is corrected by 1063 / 1024, Section 2.3. Table 1 illustrate how the lowest bits contain computation results. The analog signal level is calculated from Section 1.2.6.

Table 1: Example of how computation results sets the lowest two LSBs.

| ADC RAW CODES <sup>1</sup> | GAIN CORRECTION | DIGITAL CODE<br>LEVEL <sup>2</sup> | ACTUAL ANALOG<br>RANGE | ANALOG LEVEL <sup>3</sup> |

|----------------------------|-----------------|------------------------------------|------------------------|---------------------------|

| 0x0000                     | 1063 / 1024     | 0x0000                             | 1 Vpp                  | 0.0 mV                    |

| 0x0004                     | 1063 / 1024     | 0x0004                             | 1 Vpp                  | 0.061mV                   |

| 0x0008                     | 1063 / 1024     | 0x0008                             | 1 Vpp                  | 0.122 mV                  |

| 0x000B                     | 1063 / 1024     | 0x000B                             | 1 Vpp                  | 0.168 mV                  |

| 0x0010                     | 1063 / 1024     | 0x0011                             | 1 Vpp                  | 0.259 mV                  |

| 0x0014                     | 1063 / 1024     | 0x0015                             | 1 Vpp                  | 0.320 mV                  |

| 0x0018                     | 1063 / 1024     | 0x0019                             | 1 Vpp                  | 0.381 mV                  |

| 0x001B                     | 1063 / 1024     | 0x001C                             | 1 Vpp                  | 0.427 mV                  |

- 1. This is the raw codes from the ADC. It is 14 bits MSB aligned in 16 bit word. The 2 LSBs are thus 0.

- 2. This is the result from the gain compensation. The 2 LSBs now contain a fractional result from the computation.

- 3. This is the corresponding analog signal that was present at the input at the time of measurement. See Section 1.2.6 for details on how this is calculated.

# 1.2.2 Calibration

During the factory calibration procedure the analog properties are measured and parameters for a digital compensation are computed. An analog deviation in the front-end is thus compensated for by the inverse function in the digital signal processing part.

Example 2: With the variable gain –VG option (ADQ14), the user requests a range. The closest available setting is selected and the actual range is returned to the user for being used in the user's algorithms, see Section 2.1.

Example 3: The full scale signal range of the ADQ is measured in production and the SetGainAndOff-set function is used for adjusting to the correct signal range.

#### 1.2.3 Data acquisition nomenclature

Table 2 defines some key data acquisition terms.

Table 2: Data recording nomenclature.

| PARAMETER                                                                      | DESCRIPTION                                                                                                                                                                                                                       | REF      |

|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| ADQ                                                                            | Collective name for digitizers from Teledyne SP Devices.                                                                                                                                                                          |          |

| Analog Analog signal is the input to the ADQ14. This is the signal to be digit |                                                                                                                                                                                                                                   |          |

| Waveform                                                                       | Analog signal with a distribution in time. This is digitized into a record.                                                                                                                                                       |          |

| Sample                                                                         | An analog signal level is digitized into a sample, that is a numerical value.                                                                                                                                                     |          |

| SYNC                                                                           | Physical connector on the front panel. <sup>1</sup>                                                                                                                                                                               | 4.7, 6.1 |

| Record                                                                         | A set of consecutive samples is called a record. An analog waveform is digitized into a record of samples.                                                                                                                        | 4        |

| TRIG                                                                           | Physical SMA connector on the front panel.                                                                                                                                                                                        | 4.7, 6.1 |

| Trigger                                                                        | Trigger is a real-time event that starts acquisition of a record.                                                                                                                                                                 | 4.2      |

| Timestamp                                                                      | Timestamp is a real-time value that identifies when a trigger happened. The timestamp gives timing information for each sample.                                                                                                   | 4.3      |

| GSPS                                                                           | Giga-samples per second (10 <sup>9</sup> ). Clock frequency [Hz] and sample rate [SPS] are both used to denote speed.                                                                                                             |          |

| MSPS                                                                           | Mega-sample per second (10 <sup>6</sup> ).                                                                                                                                                                                        |          |

| DC-offset                                                                      | This is an analog DC level which is added to the analog input signal inside the digitizer to vertically move the analog signal to fit within the range of the digitizer. This effectively doubles the ENOB for a unipolar signal. | 2        |

<sup>1.</sup> Except for ADQ14-PCIe that has SYNC input and output on two MCX connector on the top side of the PCB inside the PC cabinet, see [1].

#### 1.2.4 ADQ14 sampling clock frequency

Each model of ADQ14 is designed for the specified clock frequency only. A different sampling rate can be achieved by using the sample skip function, **Section 5.9**.

The ADQ14 is available in three different speed grades, 500 MSPS, 1 GSPS and 2 GSPS. The speed grade decided when ordering the ADQ14. See ADQ14 datasheet for order codes.

Some parts of the descriptions and examples are done for only one of these frequencies. The examples are translated to the other sample rates by multiplying or dividing with the corresponding sample rate ratio.

#### 1.2.5 System clocks

The different parts of the digitizer operate on different clock rates

The sampling of the analog signal is done on the sampling clock of the ADC (see Section 1.2.4).

The external trigger input has a trigger clock which is higher than the sample clock for high trigger time precision (8 GHz).

The different host PC connections (USB, PCIe etc) has their own respective clock system.

All other interfaces operate on the data processing clock of the FPGA at 250 MHz. This clock is referred to as the Data Clock.

See Section 5.1 for more details on the clock system.

#### 1.2.6 Analog signal range

The analog signal range (ACTUAL\_ANALOG\_RANGE) is symmetrical around zero. The value of the analog signal range it is model dependent. With for example a range of, 500 mV<sub>pp</sub>, the analog input signal can vary from –250 mV to +250 mV and the range can be moved from [–0 mV +500 mV] to [–500 mV +0 mV] by the DC-offset feature, Section 2.2.

The maximum digital code 2^15 represents an analog signal with a level ACTUAL\_ANALOG\_RANGE / 2 at the input. A specific analog signal ANALOG\_LEVEL will then be represented by the following digital code:

A specific code **DIGITAL\_CODE\_LEVEL** then represent the analog level as:

# 2 SETTING UP THE ANALOG FRONT-END

# 2.1 ADQ14 AFE block diagram

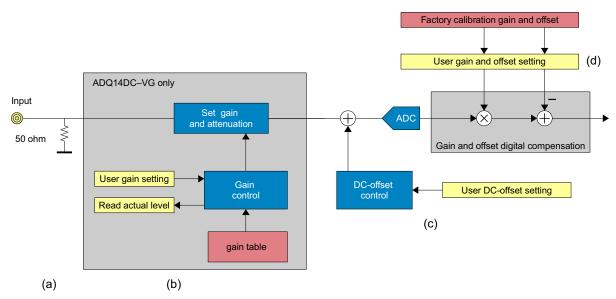

The analog front-end setup for ADQ14 found in Figure 2.

| # | DESCRIPTION                                                                                                                                                                                                                                                                                                                                           | USER COMMAND      | REF |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----|

| а | The analog input is terminated 50 ohms to GND                                                                                                                                                                                                                                                                                                         |                   |     |

| b | On ADQ14DC-VG, the gain can be set in a discrete number of steps. By requesting a certain range, the closest available setting is activated. The actual range that is set is returned to the user. Note that the compensation has to be done in the software.  Changing the input range requires a settling time of 1 s.                              | SetInputRange     | 2.1 |

| С | Set a DC offset for better using the signal range when the signal is unipolar. Changing the DC offset requires a settling time of 1 s.                                                                                                                                                                                                                | SetAdjustableBias | 2.2 |

| d | The gain and offset is calibrated using a 32 MHz -1dBFS sine wave signal. The digital compensation corrects the offset and the gain at this frequency.  The user can access this block to set a different gain and offset. Note that this is a digital gain and offset adjustment and not the same as selecting analog input range in the –VG option. | SetGainAndOffset  | 2.3 |

Figure 2: ADQ14 AFE control.

On ADQ14DC with the –VG option, the input range is variable. The requested input signal range is sent to the API, which reads available settings and return the best selection. The actual value of each range is available for calculations according to the following:

**DESIRED\_ANALOG\_RANGE** is the requested range set *into SetInputRange*.

ACTUAL\_ANALOG\_RANGE is the actual calibrated range of the device returned from SetInputRange. The maximum digital code 2^15 represents an analog signal with a level ACTUAL\_ANALOG\_RANGE / 2 at the input. A specific analog signal ANALOG\_LEVEL will then be represented by the following digital code:

A specific code DIGITAL\_CODE\_LEVEL then represent the analog level as:

# 2.2 Set analog DC-offset

A user-controlled DC-offset is available. The analog DC-offset is applied to the signal to better adopt to the signal range of the digitizer. The analog range is by default set symmetrical around zero. If the signal is unipolar or heavily unsymmetrical, the DC-offset function can adjust the signal to an optimal vertical position for the A/D converter. In this way, the full 14 bits can be used for representing the unipolar pulse. The DC-offset is set with the command <code>SetAdjustableBias</code>.

The DC-offset is set in digital codes *DC\_OFFSET\_CODE* in the range [-2^15: 2^15-1], which correspond to an analog signal level in the range:

To determine the parameter of SetAdjustableBias to get a DC-offset at the voltage level DC\_OFF-SET ANALOG, use:

Since the digitizer has higher resolution than the intrinsic accuracy of the DC-offset generator, the actual digital codes read out from the ADQ may differ from the expected level. For accurate baseline measurements, the Digital Baseline Stabilizer (DBS) offers a digital correction of the baseline to an accuracy of 22 bits, **Section 3.1**.

# 2.3 Adjusting the digital gain and offset

The digital gain and offset block is primarily intended for factory calibration but it may also be accessed by the user, and offers an efficient way of scaling the signal to suit processing in the PC.

The default setting is the calibration parameters *CAL\_GAIN* and *CAL\_OFFSET*. The raw data from the A/D converter, *ADC RAW CODE*, is corrected with the calibrated values according to:

The user can override these settings by using the software command **SetGainAndOffset**. The parameter **USER\_GAIN** and **USER\_OFFSET** can be applied in two ways; relative to the calibrated value or relative to the raw code.

The normal mode of operation is to apply the gain and offset settings relative to the calibrated data as

By setting bit 7 in the channels parameter, the calibration data is overridden as:

To get the raw code, ADC\_RAW\_CODE, use SetGainAndOffset(128+CHANNEL,1024,0).

# 3 SIGNAL QUALITY ENHANCEMENT

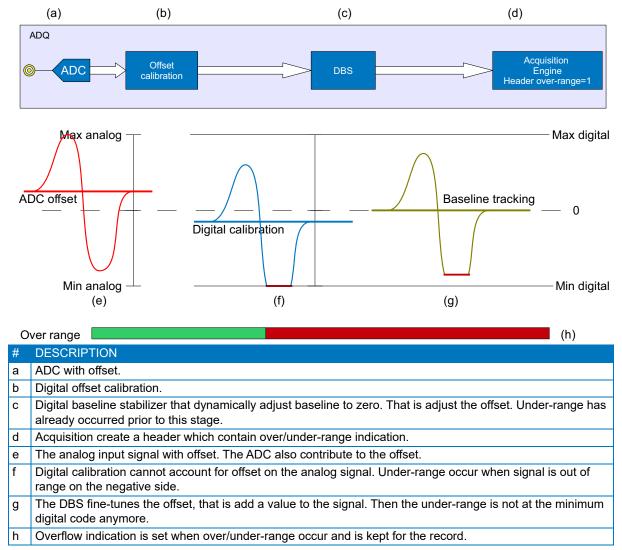

# 3.1 Digital Baseline Stabilizer

The Digital Baseline Stabilizer, DBS, is designed for pulse data measurement where high accuracy relative a known baseline is required. The key features of DBS are:

- Tracks and compensates for baseline variations from, for example, temperature and aging.

- Suppresses pattern noise<sup>1</sup> to 22 bits precision.

- Automatically locks the baseline to a user defined-value.

Note that DBS is off at power up. DBS has to be activated by the user's application software. The time when DBS is activated is important. To get a good initial estimate, DBS should be activated when there is very little signal energy present at the input. If there is too much signal power in the initial estimate, the convergence of DBS is slowed down.

Note that DBS is defined for systems with a baseline and distinct short pulses. DBS is not intended for sinusoidal type of signals. For sinusoidal types of signals use ADX, **Section 3.2**.

# 3.2 Interleaving correction ADX

The Interleaving correction ADX is available on the interleaved 2 GSPS versions of the ADQ14 (option –1X and –2X) when using firmware –FWSDR.

The ADX automatically corrects for interleaving mismatch in gain, offset, and timing in the ADC cores. The ADX also compensates for variation over frequency.

At start-up, ADX is loaded with factory calibrated settings but the correction is by-passed. Control ADX by the commands SetInterleavingIPEstimationMode and SetInterleavingIPBypassMode.

Note that DBS has to be switched off if ADX is used.

Note that ADX is intended for systems with high energy in concentrated frequency bands, like radio channels.

<sup>1.</sup> Pattern noise is systematic errors that may arise from the actual design of the ADC IC or the board design.

# 4 TRIGGER

# 4.1 Trigger block diagram

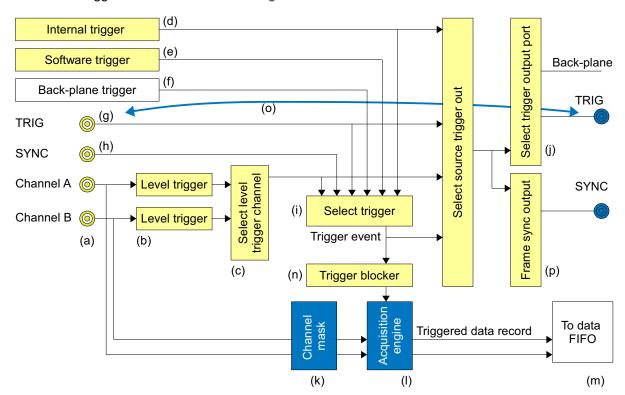

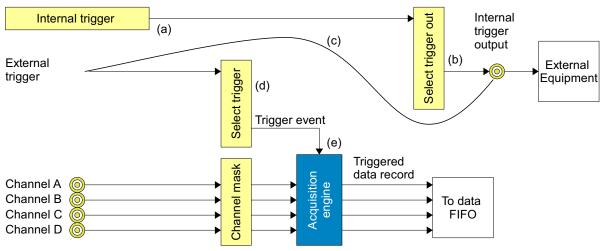

The digitizer can be triggered in various ways with a number of different internal and external trigger sources. Selected events in the trigger module can also be output to trigger external equipment. The selection of trigger source is illustrated in **Figure 3**.

| # | DESCRIPTION                                                                                                             | USER COMMAND                                 | REF    |

|---|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------|

| а | Connectors for external analog input signals. The number of channel vary on the different models and configurations.    |                                              |        |

| b | Each analog input is connected to a level trigger block.                                                                | SetupLevelTrigger                            | 4.9    |

| С | Select on which channel to trigger (when using level trigger).                                                          | SetupLevelTrigger                            | 4.9    |

| d | Internal trigger generator.                                                                                             | SetInternalTriggerPeriod                     | 4.10   |

| е | A software trigger is available for user control.                                                                       | SWTrig                                       | 4.6    |

| f | External trigger input from backplane in PXIe or MTCA.                                                                  |                                              | 4.8    |

| g | External trigger input on front panel connector TRIG.                                                                   |                                              | 4.7.1  |

| h | External trigger input on front panel connector SYNC.                                                                   |                                              | 4.7.2  |

| i | Select which type of trigger to activate.                                                                               | SetTriggerMode                               |        |

| j | Activate trigger output.                                                                                                | SetupTriggerOutput                           | 4.11   |

| k | Select which channels to record data from.                                                                              | SetStreamConfig<br>MultirecordSetChannelMask |        |

| I | Acquisition engine creates a record from streaming data                                                                 |                                              | 7      |

| m | Records are sent to data FIFO for transfer to the host PC                                                               |                                              | 7      |

| n | The trigger blocking function controls the flow of triggers to the acquisition engine.                                  | SetupTriggerBlocking                         | 4.4    |

| 0 | Note that the trigger output and the external trigger input are physically the same connector on the front panel: TRIG. |                                              |        |

| р | Frame sync is a function that can group triggers.                                                                       | SetupFrameSync                               | 4.11.2 |

Figure 3: Trigger source selection and setup illustrated for a 2 channels mode.

# 4.2 Position of the trigger in the data

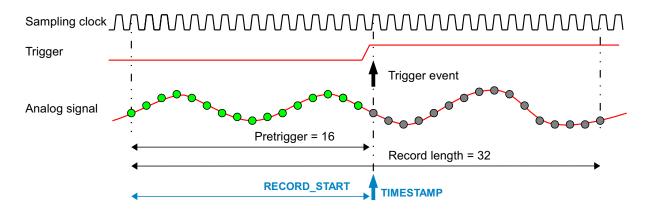

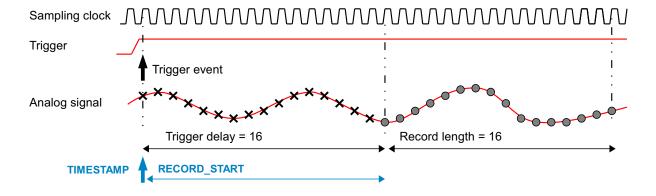

The trigger position relative to the data record is controlled by the parameters pretrigger and trigger delay.

The pretrigger buffer enables capturing data prior to the trigger event, **Figure 4**. Use the command **Set-PreTrigSamples** to define the pretrigger.

The trigger delay postpone the start of the acquisition of the data record specified number of samples after the trigger event, **Figure 5**. Use the command **SetTriggerHoldOffSamples** to define the trigger delay.

The timing of the trigger is read from the record header (Section 7.6). The parameters TIME\_STAMP and RECORD START are explained in Section 4.3.1.

Figure 4: Pretrigger timing.

Figure 5: Trigger delay timing.

#### 4.3 Timestamp

# 4.3.1 Timestamp definitions

The timestamp counter enables real-time measurement of a trigger event. It is used for tagging an event, sorting events in time or comparing timing between events.

The timestamp information consist of three parts, which uniquely defines the timing:

- TIME STAMP measures the time of the trigger event relative to other trigger events.

- **RECORD\_START** is the time between the trigger event and the start of the record. For a pretrigger, this is a negative value. When trigger delay is used, this is a positive value.

• **SAMPLE\_PERIOD** is the length of a sample period. The sample period may vary with sample skip setting and clock frequency of the digitizer.

The *TIME\_STAMP*, *RECORD\_START*, and *SAMPLE\_PERIOD* are measured in the unit *TIME\_BASE* = 125 ps. See Example 4 on how to use these parameters. These parameters are available in the record header, see Section 7.6.1.

The timestamp counter is based on the internal clock of the digitizer. The internal clock is based on the selected clock reference. The timestamp is thus also related to the clock reference. When the clock reference is phase-locked to an external source, the timestamp counter is running synchronized with the external source. On the other hand, if the digitizer is free running, the timestamp counter also free running. (See **Section 5** for all details about the clock system of digitzer.)

The timestamp counter measures the time from a reference time point to the trigger event. The reference time point is when the counter is started or reset. See **Section 4.3.2** for information on how to reset the timestamp counter.

Example 4: Assume an ADQ14 sampling with a clock frequency at 1 GSPS. The pretrigger is set to 16 samples and the external trigger is used. The following parameters are returned:

```

TIME_STAMP = 1001

RECORD_START = -129

SAMPLE_PERIOD = 8

TIME_BASE = 125 ps

```

The time for the trigger was then

TRIGGER TIME = TIME STAMP \* TIME BASE = 125125 ps = 125.125 ns

The time for the first sample in the record is

RECORD TIME = (TIME STAMP + RECORD START) \* TIME BASE = 109.000 ps = 109 ns

The time between two samples are SAMPLE\_TIME = SAMPLE\_PERIOD \* TIME\_BASE = 1 ns

The time from the record start to the trigger is  $RECORD\_START * TIME\_UNIT = -16.125 \text{ ns.}$

The number of samples between the record start and the trigger event is (TRIGGER\_TIME - RECORD\_TIME) / SAMPLE\_TIME = | RECORD\_START | / SAMPLE\_PERIOD = 16.125 samples

This is the expected 16 samples set in the pretrigger and 1/8 sample in subsample precision in the external trigger.

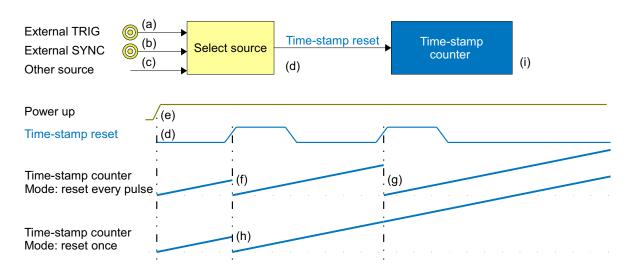

#### 4.3.2 Timestamp reset

When powering up a system with many boards, the timestamp counter in each board will start. But the counters start at different times in different physical digitizers. There are four methods for resetting the timestamp and get a common time reference in all the digitizers in the system:

- The timestamp counter is reset at power-up. This methods does not, however, have absolute precision, since the timing of the power up is not defined. In a multi-board system, the timestamp will differ between the boards.

- 2. With a software reference reset the user has full control of the reset procedure. A reference time point is created in the users application, which is used for aligning time-stamps in different units. After power-up the user runs a custom timestamp reset sequence including:

- · Apply a reference signal to all boards.

- · Trigger a record on the reference signal.

- Read the time-stamps from the records and call this reference; TIME STAMP REFERENCE.

- Start the experiment and subtract the timing reference from each record as TIME\_STAMP = TIME\_STAMP\_OF\_RECORD - TIME\_STAMP\_REFERENCE.

- 3. The third method is to apply an external trigger to reset the timestamp reset, **Figure 6**. This method has the possibility to synchronize several boards to full precision of the external trigger. See **Section 4.4**. The sequence of operation is:

- DisarmTimestampSync

- SetupTimestampSync

- ArmTimestampSync

The number of reset pulses are counted and the information is stored in the record header, **Section 7.6**. However, if there are no triggers accepted, there will be no record headers available. To verify that there is activity going on, the number of reset pulses can also be read from a register via **GetTriggerBlockingGateCount**.

4. The fourth method is to reset the timestamp with the sync signal, **Figure 6**. The difference between using the external trigger and the sync is that the external trigger has the a sample resolution while the sync timing resolution is controlled by the Data Clock in the FPGA. Note that the backplane triggers in –PXIe and –MTCA formats work in the same way as the sync signal.

| # | DESCRIPTION                                                           | USER COMMAND           | REF   |

|---|-----------------------------------------------------------------------|------------------------|-------|

| а | External trigger input signal on front panel connector.               |                        | 4.7   |

| b | External sync input signal on front panel connector.                  |                        | 4.7   |

| С | Other available sources (see SetTriggerMode for a list)               |                        | 4.7   |

| d | Select source for reseting timestamp.                                 | SetupTimestampSync     | 4.3.2 |

| е | Timestamp counter value is reset at power-up of the digitizer.        | DisarmTimeStampSync    | 4.3.2 |

| f | Reset the timestamp counter on each pulse of the selected source.     | ArmTimeStampSync       | 4.3.2 |

| g | Timestamp is then measuring time relative the previous reset signal.  |                        | 4.3.2 |

| h | Reset the timestamp counter only on the first pulse of the selected   |                        | 4.3.2 |

|   | signal. The external signal is then a systems synchronization signal. |                        |       |

| i | The number of times the time stamp has been reset can be read from    | GetTriggerBlockingGate | 4.3.2 |

|   | a register.                                                           | Count                  |       |

Figure 6: Timestamp reset from external trigger.

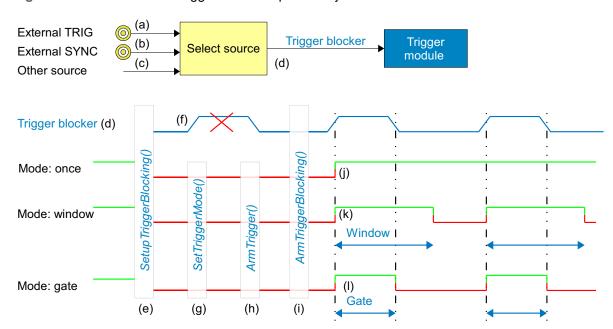

# 4.4 Blocking triggers for synchronization

#### 4.4.1 Function overview

In order to synchronize the acquisition to external equipment or to other ADQ digitizers, there is a mechanism for controlling the flow of triggers. The trigger blocking function allows the user to select when to activate incoming triggers, **Figure 7**. The basic function of this block is to use the SYNC signal to frame the trigger signals; for each period of the blocking function, a set of triggers are allowed and and framed by the blocking event. This creates groups of triggers that belong together. The modes of operation for trigger blocking are shown in **Figure 7** (j, k, l).

To avoid that the boards start to produce a large amount of records out of sync, all trigger events can be blocked until the triggers are released by a separate shared signal, **Figure 7** (d). By combining the trigger blocking and the timestamp reset, the timestamp is aligned to the start of the acquisition. The trigger blocker source can be most available trigger sources, **Figure 7** (a, b, c).

Note the order of the commands for activating triggers and trigger blockers, Figure 7 (e, g, h, i).

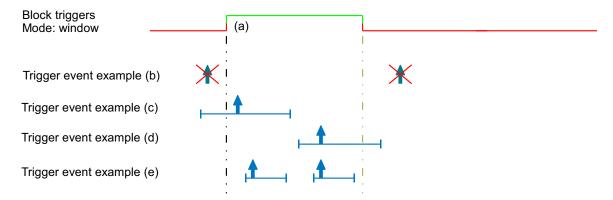

Figure 8 illustrates how the triggers are accepted or rejected in the window mode.

| # | DESCRIPTION                                                                                                         | USER COMMAND         | REF   |

|---|---------------------------------------------------------------------------------------------------------------------|----------------------|-------|

| а | External trigger input signal on front panel connector.                                                             |                      | 4.7   |

| b | External sync input signal on front panel connector.                                                                |                      | 4.7   |

| С | Other available sources (see SetTriggerMode for a list).                                                            |                      |       |

| d | Select source for blocking triggers.                                                                                | SetupTriggerBlocking | 4.4   |

| е | Before activating the trigger blocking any selected trigger may pass.                                               | SetupTriggerBlocking |       |

| f | This signal is ignored as the trigger blocker is not armed                                                          |                      |       |

| g | Select trigger source                                                                                               | SetTriggerMode       |       |

| h | Start receiving triggers. Note that triggers are still blocked.                                                     | ArmTrigger           |       |

| i | The unblocking of triggers is armed and can be activated by (d).                                                    | ArmTriggerBlocking   |       |

| j | Triggers are blocked until the first accepted blocker signal.                                                       | SetupTriggerBlocking | 4.4   |

| k | The trigger blocker can also be set up with a window function where                                                 | SetupTriggerBlocking | 4.4.1 |

|   | triggers are accepted or rejected during a user-defined window.                                                     |                      |       |

| I | The trigger blocker can also be set up as a gate where triggers are accepted during a gated time set by signal (d). | SetupTriggerBlocking | 4.4.1 |

Figure 7: Blocking and gating of triggers.

| # | DESCRIPTION                                                                                                             | USER COMMAND         | REF   |

|---|-------------------------------------------------------------------------------------------------------------------------|----------------------|-------|

| а | The trigger blocker in window or gate mode allows triggers during a certain period.                                     | SetupTriggerBlocking | 4.4.1 |

| b | Example of rejected triggers outside the window.                                                                        |                      |       |

| С | Trigger within the window is accepted and a data record is recorded. Note that the pretrigger starts before the window. |                      |       |

| d | Trigger within the window is accepted and a data record is recorded. Note that the record extends after the window.     |                      |       |

| е | Several triggers within the same window.                                                                                |                      |       |

Figure 8: Trigger blocker examples.

# 4.4.2 Block triggers once

The mode for blocking triggers once is illustrated in **Figure 7** (j). This mode is used for starting the operation simultaneously in several units. The first time the trigger blocking signal is applied, the triggers are allowed through. Here is the motivation for this mode:

There is no way to broadcast a software command to several units. When setting up acquisition in several units, they will therefore be activated at different times. By using the trigger blocker, an electrical signal to all units can activate them simultaneously. The trigger blocking signal can be external or it can be generated internally using the bussed connections proposed in **Figure 13**.

### 4.4.3 Windowing triggers

The window mode for blocking triggers is illustrated in **Figure 7** (k). The edge of the trigger blocking signal is activating a window of user-defined length which allows triggers through. There is also a mode where triggers are blocked during the window.

The window mode can be used for two-dimensional triggering where, for example, the trigger signal is a point trigger and a sync signal is a line trigger.

# 4.4.4 Gating and windowing triggers

The gate mode for blocking triggers is illustrated in **Figure 7** (I). The length of the window where triggers are accepted is equal to the length of the trigger blocking signal.

#### 4.4.5 Programming sequence for using trigger blocking

The order of commands is important when programming the trigger blocking. This is because the ADQ digitizer interact with other external equipment. This external equipment is synchronized to the digitizer through the setup procedure.

The setup of the functions has to be aligned with the expected operation. For example, by asserting the trigger blocking through the **SetupTriggerBlocking** command before setting up the acquisition, no triggers are let through before the digitizer is ready.

The function on the digitizer has to be activated (armed) in reverse order compared to the data flow. This means that one stage is set up to be prepared to receive data before the preceding stage is set up to generate data. This is especially important in streaming applications where the DRAM FIFO may overflow if the triggering is activated before the read-out to the host PC has started.

# 4.5 Trigger jitter

#### 4.5.1 Trigger jitter definitions

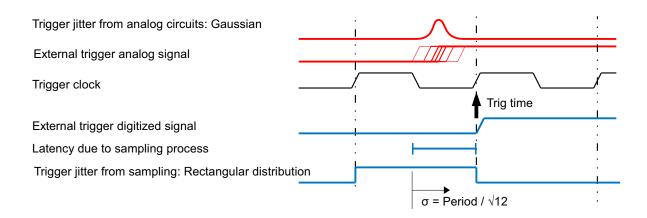

The triggering operation is subject to two different types of jitter, Figure 9.

- At the trigger input is a Gaussian distributed jitter which affects the timing of the incoming trigger signal edge. This jitter is called excess jitter and is caused by noise in the input stage. The RMS value of this excess jitter is 25 ps.

- 2. The actual sampling process causes a timing uncertainty. Since the trigger is sampled with the trigger clock, the time points for reading the trigger are discrete. The difference between the incoming physical trigger signal and the digital representation of the trigger is a stochastic variable with a rectangular distribution. The RMS value of such a process is TRIGGER\_CLOCK\_PERIOD/sqrt(12). The highest resolution is achieved with an external trigger connected to the TRIG connector. ADQ14 has a trigger clock at 8 GSPS, TRIGGER\_CLOCK\_PERIOD of 125 ps and a trigger jitter of 36 ps RMS (theoretical value), Section 4.5.4.

See **Table 3** for time resolution all the external trigger sources.

Figure 9: Sources of jitter on the trigger signal.

#### 4.5.2 Asynchronous triggering

If the trigger signal is not phase-locked to the reference clock it is called asynchronous. This trigger does not have a well-determined relation to the sampling clock and will appear at various positions within the sampling period. The time resolution of an asynchronous trigger connected to the TRIG input is set by the Trigger Clock (8 GHz). The time resolution for other triggers is determined by the Data Clock (250 MHz).

The asynchronous trigger will be exposed to both trigger sources from **Section 4.5.1**. These independent stochastic processes are added to 44 ps. See **Table 3** for time resolution of all the external trigger sources.

There are some advantages with the asynchronous trigger:

- Any pattern noise will be reduced in repeated measurements.

- The trigger resolution of 125 ps can be used for accurate timing calculations. The TIME\_STAMP

contains the information about the trigger time. See Section 4.5.4.

### 4.5.3 Synchronous trigger

A synchronous trigger is phase locked to the clock of the digitizer. The trigger source needs access to the clock reference of the digitizer. There are three ways to achieve this synchronization:

- 1. Output the internal clock reference of the ADQ and send it to the trigger source, Section 5.8.

- 2. Use the clock reference of the trigger source as clock reference for the ADQ, Section 5.5.

- 3. Use the internal trigger of the ADQ and output it to trigger the external equipment, Section 4.10.

When the trigger is phase-locked to the clock reference the timing is comparable to a digital signal which defines setup and hold time.

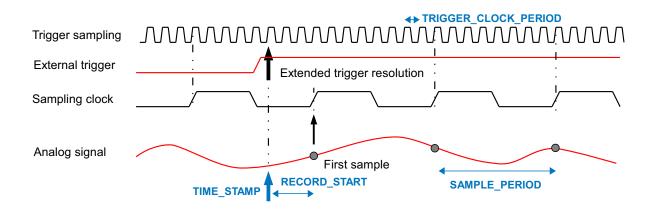

#### 4.5.4 Extended trigger resolution

The basic sampling process maps the trigger to the sampling rate of the digitizer. There is also additional trigger time information available; Extended trigger resolution, **Figure 10**.

The Trigger Clock is operating at 8 GHz. This means that the time resolution of the trigger input TRIG is reduced to 125 ps.

Note: The extended trigger resolution is available on triggers connected to TRIG only.

The extended trigger information is included in the timestamp information, Section 4.3.

Figure 10: Extended trigger resolution timing for ADQ14-4C at 1 GSPS.

The position of the first sample is rounded up from the trigger position. The parameter *RECORD\_START* tells where the trigger was. Referring to **Figure 10**, the *RECORD\_START* parameter can have values in the range –375 ns up to +500 ns. A positive value means that the first sample is after the trigger. The given range is without pretrigger or trigger delay. With pretrigger or trigger delay, the *RECORD\_START* will have a larger (absolute) value.

#### 4.6 Software trigger

The software trigger is a user command that triggers the ADQ. This is for direct user control of the acquisition and is useful for looking at continuous signals where the timing of the trigger is not critical. The software trigger is sent through several layers of software and the time when it arrives to the ADQ14 cannot be predicted. However, the time when it actually arrived can be read from the time stamp in the record header. **Section 4.3**.

The software trigger may also be used for time-out function. This is a way to discover faults in the setup. When the device do not trigger for some reason within a certain time frame, a software command sequence may be sent and the data can be analyzed to find out what is wrong, **Example 4**.

Example 4: A time-out function using software trigger can be implemented like this:

1. Time-out occurs

- 2. DisArmTrigger

- 3. SetTriggerMode("software trigger")

- 4. ArmTrigger

- 5. SWTrig

- 6. Read data and analyze the situation

# 4.7 External Trigger Inputs

An external trigger is a dedicated signal on a dedicated input to the ADQ. There are several inputs for external trigger, **Table 3**.

| CONNECTOR | DESCRIPTION                                                      | TIME<br>RESOLUTION | TOTAL<br>JITTER | IMPEDANCE           | TRIG<br>LEVEL    | REF   |

|-----------|------------------------------------------------------------------|--------------------|-----------------|---------------------|------------------|-------|

| TRIG      | External trigger on front panel.                                 | 125 ps             | 44 ps           | 50 Ω / 500 Ω        | SW contr.        | 4.7.1 |

| SYNC      | Sync signal on front panel.                                      | 4 ns               | 1.2 ns          | 50 Ω / 500 Ω        | 1.5 V            | 4.7.2 |

| STARB     | Backplane trigger in PXIe systems. Requires trigger timing card. | 4 ns               | 1.2 ns          | PXIe standard       | PXIe<br>standard | 4.8.1 |

| MLVDS     | Backplane trigger in MVLDS systems.                              | 4 ns               | 1.2 ns          | MLVDS.4<br>standard | MLVDS.4 standard | 4.8.2 |

Table 3: External trigger inputs.

#### 4.7.1 External trigger TRIG front panel connector

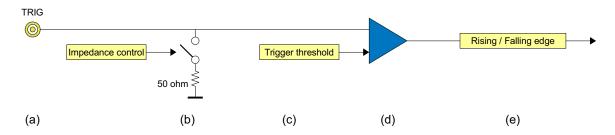

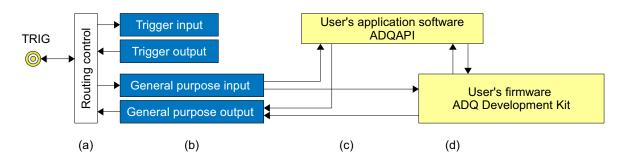

The block diagram for the TRIG is shown in **Figure 11** and related parameters are listed in **Table 3**. The user can control the external trigger function for adapting it to the system in the following ways:

- The input impedance can be set in 50  $\Omega$  (default) or high impedance mode, see **Section 4.7.3**.

- · Configure the threshold level.

- Set the trigger edge to rising or falling to adjust to the polarity of the trigger signal.

| # | DESCRIPTION                                                                             | USER COMMAND             | REF   |

|---|-----------------------------------------------------------------------------------------|--------------------------|-------|

| а | The input is available on an SMA connector on the front panel.                          |                          |       |

| b | The input impedance can be set as 50 $\Omega$ (default) or high impedance 500 $\Omega.$ | SetTriggerInputImpedance | 4.7.3 |

| С | The trigger threshold is 0.5 V (default) and user-controlled.                           | SetExtTrigThreshold      |       |

| d | High speed comparator.                                                                  |                          |       |

| е | Select rising or falling edge.                                                          | SetExternTrigEdge        |       |

Figure 11: External trigger on front panel.

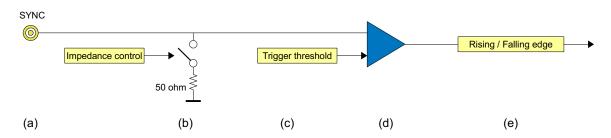

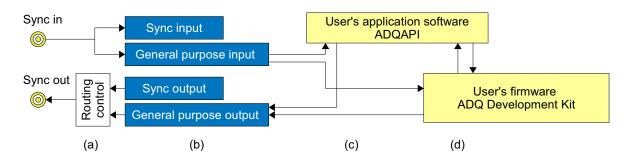

#### 4.7.2 External trigger SYNC connector

The block diagram for the SYNC input is shown in **Figure 12** and related parameters are listed in **Table 3**. The user can control the SYNC function for adapting it to the system in the following ways:

- The input impedance can be set in 50  $\Omega$  (default) or high impedance mode, see Section 4.7.3.

- Set the trigger edge to rising or falling to adjust to the polarity of the trigger signal.

| # | DESCRIPTION                                                                                                                                                 | USER COMMAND             | REF   |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------|

| а | The input is available on an SMA connector on the front panel. For ADQ14–PCle it is an MCX connecor on the top side of the digitizer inside the PC cabinet. |                          |       |

| b | The input impedance can be set as 50 ohm (default) or high impedance.                                                                                       | SetTriggerInputImpedance | 4.7.3 |

| С | The trigger threshold is fixed at 1.5 V.                                                                                                                    |                          |       |

| d | High speed comparator.                                                                                                                                      |                          |       |

| е | Select rising or falling edge.                                                                                                                              | SetExternTrigEdge        |       |

Figure 12: Using SYNC as trigger input.

#### 4.7.3 Driving the external TRIG/SYNC signal by controlling input impedance

The TRIG/SYNC input impedance is by default 50  $\Omega$ . The trigger is optimized for systems where the trigger source output impedance is 50  $\Omega$  and the cables has a characteristic impedance of 50  $\Omega$ . This setup results in an optimal high-frequency response and low reflections, which is important for precise timing.

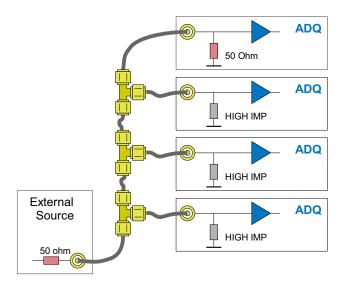

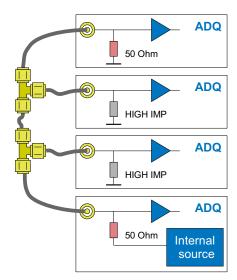

However, in a high fan-out situation, where a trigger source has to drive many nodes, the load can be too high. The trigger input can then be set in a high impedance mode and a bussed connection can be used, **Figure 13** (a) an external source is driving the array of ADQ digitizers. In **Figure 13** (b) one of the ADQ digitizer is used as a master and is driving signals to the array of ADQ digitzers. One has to be careful with the trigger distribution network to handle the reflections. If the trigger is periodic, reflections are less critical and can be handled. For more information on reflections, see application note [8].

(a) External source

(b) ADQ internal source

Figure 13: Bussed connections

# 4.8 External trigger in the backplane

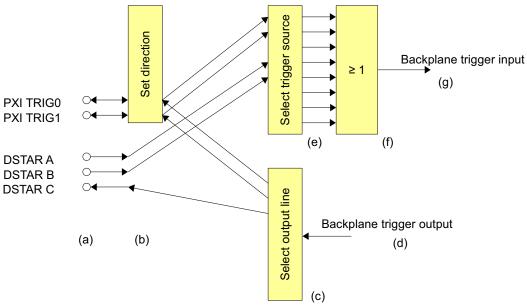

#### 4.8.1 PXIe interface

There are an external trigger in the backplane of the PXIe version of ADQ14. The DSTAR signals are dedicated matched trigger lines from the system timing slot. To use these triggers, a dedicated timing generation board has to be used in the system timing slot. The TRIG bus is a general bus in the backplane which can be used for triggering. The ADQ support connection to port 0 and port 1 of that bus.

The backplane trigger support both input and output triggers. These operations are independent and can be used simultaneously.

| # | DESCRIPTION                                                          | USER COMMAND       | REF  |

|---|----------------------------------------------------------------------|--------------------|------|

| а | Backplane Trigger bus and DSTAR connections                          |                    |      |

| b | Set direction for each port in the backplane                         | SetDirectionPXI    |      |

| С | Output: Select output port for trigger output signal                 | SetupTriggerOutput | 4.11 |

| d | Output: This is the source for the trigger output signal             | SetupTriggerOutput | 4.11 |

| е | Input: Select port for trigger sources                               | SetTriggerMaskPXI  |      |

| f | Input: The backplane trigger signal is OR:ed from the selected ports |                    |      |

| g | Input: this is the backplane trigger to the trigger module           | SetTriggerMode     | 4.1  |

Figure 14: Trigger in the PXIe backplane.

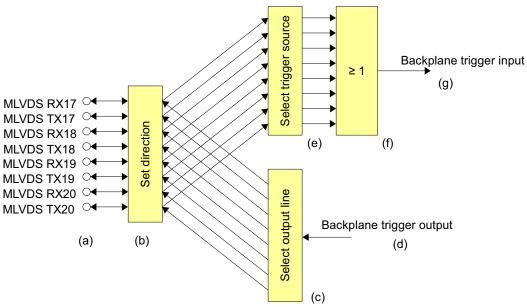

### 4.8.2 MTCA.4 interface

The MLVDS lines, port 17 to 20, can be used as trigger input or output, **Figure 15**. The backplane trigger support both input and output triggers. These operations are independent and can be used simultaneously.

| # | DESCRIPTION                                                          | USER COMMAND        | REF  |

|---|----------------------------------------------------------------------|---------------------|------|

| а | Backplane MLVDS bus                                                  |                     |      |

| b | Set direction for each port in the backplane                         | SetDirectionMLVDS   |      |

| С | Output: Select output port for trigger output                        | SetupTriggerOutput  | 4.11 |

| d | Output: This is the source for the trigger output signal             | SetupTriggerOutput  | 4.11 |

| е | Input: Select port for trigger sources                               | SetTriggerMaskMLVDS |      |

| f | Input: The backplane trigger signal is OR:ed from the selected ports |                     |      |

| g | Input: this is the backplane trigger to the trigger module           |                     | 4.1  |

Figure 15: MLVDS port 17 - 20 as trigger signals.

# 4.9 Level trigger

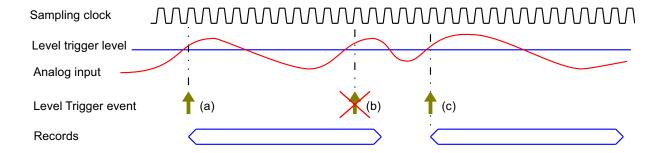

The level trigger allows data-driven acquisition. When the data on a selected channel crosses the trigger level, all channels on the ADQ is triggered<sup>1</sup>, **Figure 16**. The level trigger is set to trigger on rising or falling edge. Here, rising edge is illustrated.

<sup>1.</sup> Firmware option FWPD offers a channel independent level trigger. See specific documentation in form of user guides [7] and application note [6].

| # | DESCRIPTION                                                                                                                                                          | USER COMMAND      | REF   |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------|

| а | When the signal passes the trigger level, a trigger event is generated and the first record is captured.                                                             | SetupLevelTrigger | 4.9.1 |

| b | During the record, incoming triggers are ignored.                                                                                                                    |                   |       |

| С | When the signal passes the trigger level, a trigger event is generated and the second record is captured. Re-triggering is also controlled by a hysteresis function. | SetupLevelTrigger | 4.9.3 |

Figure 16: Level trigger introduction.

#### 4.9.1 Setting the level trigger level

The level is given in digital codes:

The ACTUAL\_ANALOG\_RANGE is the analog full scale range. If a DC-offset is used at the input, add the DC\_OFFSET\_CODE from (6).

# 4.9.2 Level trigger and DBS

The Digital Baseline Stabilizer, DBS, compensates for fluctuations in the baseline. The DC level is then set by a parameter **DBS\_CODE** into DBS. The level trigger is set relative to the analog baseline as:

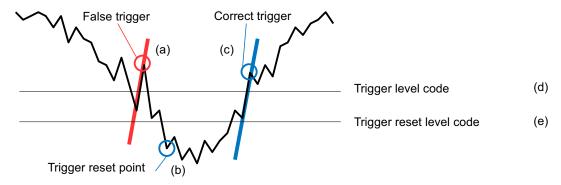

#### 4.9.3 Controlling noise sensitivity

The level trigger is sensitive to noise since it can detect a step as small as one digital code. This can cause unwanted triggering. The noise sensitivity is controlled by a hysteresis function, **Figure 17**. After triggering, the signal has to cross a reset level before it can trigger again.

Setting the reset level far from the trigger level will give a robust trigger.

Setting the reset level close to the trigger level will give a sensitive trigger.

| # | DESCRIPTION                                                              | USER COMMAND      | REF   |

|---|--------------------------------------------------------------------------|-------------------|-------|

| а | The level trigger has a hysteresis function to avoid false triggering on |                   | 4.9.3 |

|   | noise.                                                                   |                   |       |

| b | When the signal passes below the <b>RESET_LEVEL_CODE</b> , the ADQ may   |                   |       |

|   | trigger again.                                                           |                   |       |

| С | Trigger position is the first sample above the trigger LEVEL_CODE        |                   |       |

| d | Set the trigger <i>LEVEL_CODE</i> .                                      | SetupLevelTrigger | 4.9.1 |

| е | Set the trigger RESET_LEVEL_CODE.                                        | SetupLevelTrigger | 4.9.3 |

Figure 17: Trigger reset level.

# 4.10 Internal trigger

The internal trigger generates a periodic trigger signal. The internal trigger period is specified in number of samples.

Note that if the internal trigger signal used as a trigger output, the actual output signal is updated at the Data Clock rate. This may appear as jitter on the output. It is recommended to use a period that is a multiple of the Data Clock is the internal trigger shall drive external equipment.

#### 4.11 Trigger output

The trigger output signal is intended for triggering external equipment connected to the ADQ to build a synchronized system. It can also be used for indicating that a trigger event occurred in the digitizer. The trigger output is updated at the rate of the Data Clock.

The trigger output function consists of two parts:

- The first part selects the source of the trigger output signal.

- The second part selects the physical output port for the trigger output signal.

Note that the trigger output is the same physical TRIG connector as the external trigger input.

#### 4.11.1 Trigger output port selection

The trigger output port is selected to one of these ports:

- Trigger connector on the front panel. Note that the trigger output is the same physical TRIG connector as the external trigger input.

- PXIe backplane triggers, Section 4.8.1.

- MTCA.4 MLVDS triggers in the backplane, Section 4.8.2.

The availability of these ports depends on the interface option for the digitizer.

#### 4.11.2 Frame sync output on SYNC connector

The frame sync feature enables grouping of trigger signals into frames or blocks or lines. The name for this feature relate to the actual application. This function can, for example, be used in scanning three-dimensional measurements where a record is the first dimension, the trigger is the second and the frame sync is the third dimension.

The frame sync count triggers and output a signal at a certain period. The period is measured in trigger events.

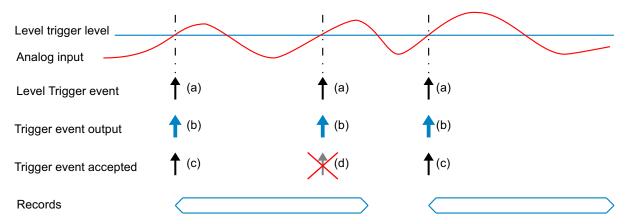

#### 4.11.3 Trigger event indicator

The trigger output can be used for indicating that trigger event occurred in the digitizer. A trigger event is some event that causes the digitizer to trigger. When used as a trigger event indicator all trigger events are presented at the trigger output port, **Figure 18** (a, b) illustrates how trigger events appear at the trigger output. The trigger events at **Figure 18** (c) will generate a record. The event **Figure 18** (d), however, occurs while the recording is ongoing and will thus not generate a record.

Note that the timing of the trigger event in the capturing of a record is based on the Sample Clock but the trigger output is based on the Data Clock.

| # | DESCRIPTION                                                                | USER COMMAND       | REF |

|---|----------------------------------------------------------------------------|--------------------|-----|

| а | Level trigger generates trigger events.                                    |                    |     |

| b | Trigger output of the the level trigger events.                            | SetupTriggerOutput |     |

| С | Accepted trigger events create records.                                    |                    |     |

| d | This trigger event is falling within the recording and is discarded by the |                    |     |

|   | acquisition control. This trigger will not create any new record.          |                    |     |

Figure 18: Trigger event output for a level triggered system.

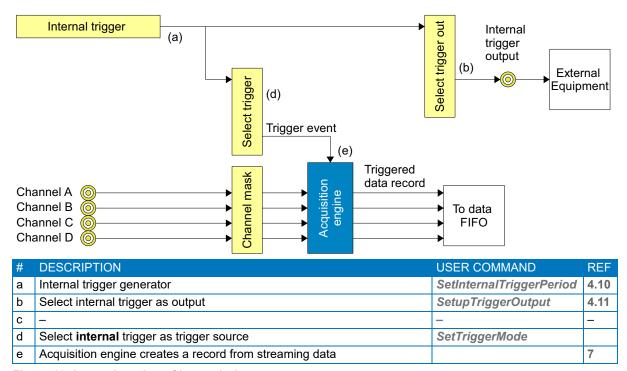

# 4.11.4 Triggering external equipment with internal trigger

Triggering external equipment and the digitizer with the internal trigger may be done in two ways; internally, **Figure 19** and externally, **Figure 20**.

The internal connection is preferred when the trigger is only used for triggering the digitizer. The triggering is then done inside the FPGA as a logical signal and the trigger time is guaranteed to be exact on the expected sample.

The external connection is preferred when the trigger is used for triggering both the digitizer and the external equipment. Then the ADQ will listen to the same physical signal as the external equipment is using.

Figure 19: Internal routing of internal trigger.

| # | DESCRIPTION                                                                                       | USER COMMAND             | REF  |

|---|---------------------------------------------------------------------------------------------------|--------------------------|------|

| а | Internal trigger generator                                                                        | SetInternalTriggerPeriod | 4.10 |

| b | Select internal trigger as output                                                                 | SetupTriggerOutput       | 4.11 |

| С | The trigger output and the external trigger input are electrically connected inside the digitizer |                          |      |

| d | Select <b>external</b> trigger as trigger source                                                  | SetTriggerMode           |      |

| е | Acquisition engine creates a record from streaming data                                           |                          | 7    |

Figure 20: External routing of internal trigger.

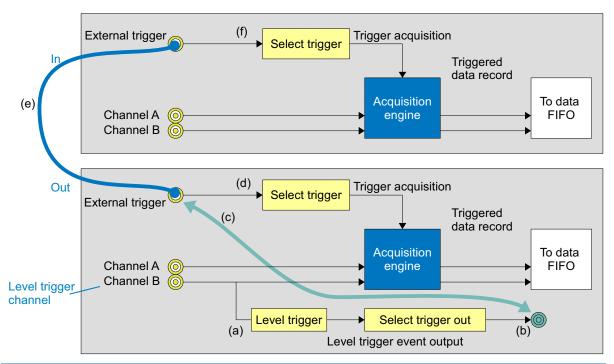

# 4.11.5 Distributing level trigger

Multiple boards may be triggered by a level trigger on one channel in one of the digitizers. This mode is intended for systems with a reference event on one channel that starts the acquisition on all channels.

It may also be used for designing a high precision trigger. The trigger event on channel D in **Figure 21** is recorded on the channel D. The trigger timing is then calculated with high precision using interpolation.

| # | DESCRIPTION                                                        | USER COMMAND       |

|---|--------------------------------------------------------------------|--------------------|

| а | Select a channel as level trigger.                                 | SetupLevelTrigger  |

| b | Select level trigger as trigger out.                               | SetupTriggerOutput |

| С | Internal hardware connection trigger out to trigger in (shared SMA |                    |

|   | connector).                                                        |                    |

| d | Select external trigger for triggering                             | SetTriggerMode     |

| е | External cable connection to other digitizers.                     |                    |

| f | Select external trigger for triggering.                            | SetTriggerMode     |

Figure 21: Distributing level trigger.

### 5 CLOCK

#### 5.1 Clock domains

Different parts of the digitizer system operate on different clocks. The core of the clocking system is the clock reference. This is the phase and frequency reference of the digitizer system. It is possible to use different clock reference sources to meet the requirements of different applications.

The sampling clock is generated based on clock reference and drive the ADCs. This clock is important for the signal quality since any timing deviation (jitter) will impact the actual time of the sample.

The trigger signal is sampled by a separate clock at a higher frequency than the sampling clock. This is to achieve a good timing resolution of the trigger. This frequency is the highest in the digitizer and is also the base for the timestamp.

The FPGA cannot operate at the high rate of the sampling clock. Instead the data processing operate on a derived lower frequency denoted Data Clock and several samples are processed in parallel to maintain the throughput. The Data Clock is also synchronized to the clock reference.

Finally the host PC interface also operate on a different clock. The PCIe system clock is provided from the PCIe bus. This part of the design is not phase-locked to the sampling clock.

| # | DESCRIPTION                                                           | TYPICAL FREQUENCIES | REF |

|---|-----------------------------------------------------------------------|---------------------|-----|

| а | Clock reference.                                                      | 10 – 500 MHz        | 5.2 |

| b | Clock generator that generates several frequencies.                   |                     | 5.6 |

| С | Various interfaces.                                                   |                     | 4.7 |

| d | The ADC operates on sampling clock.                                   | 1GHz                |     |

| е | The trigger operates on the trigger clock.                            | 8 GHz               | 4   |

| f | Other interfaces operate on the Data Clock.                           | 250 MHz             | 4 6 |

| g | The FPGA operate on the Data Clock.                                   | 250 MHz             |     |

| h | The host PC operate on an independent clock.                          | 125 MHz (PCle)      |     |

| İ | The clock generation for the host interface depend on interface type. |                     |     |

Figure 22: Clock system overview

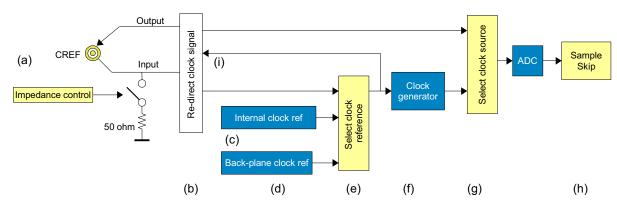

#### 5.2 Flexible clock network

The preferred clock method is a systems design parameter and teh digitizer supports many options. The clock system of the digitizer consist of two key parts; the clock reference and the clock generator. The clock reference is a low frequency (10 MHz) high-precision and high-stability signal that sets the accuracy of the clocks in the digitizer. The clock generator translates the frequency of the clock refer-

ence to the sampling clock rate. The digitizer supports its specified sample rate only. This sample rate can be tuned to allow phase locking to external equipment.

To reduce the sample-rate, a sample skip function is available.

Block diagrams of the clock network for ADQ14 is given in Figure 23.

| # | DESCRIPTION                                                                                                                                                                     | USER COMMAND                                        | REF |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----|

| а | The input SMA connector is common for external clock reference input, external clock input and external reference output. The impedance is set to 50 $\Omega$ or 200 $\Omega$ . | SetClockInputImpedance                              |     |

| b | The clock signals for the external SMA connector are re-directed according to the clock selection.                                                                              | SetClockSource                                      |     |

| С | The internal clock reference is a high performance VCTCXO.                                                                                                                      |                                                     | 5.4 |

| d | The PXIe and MTCA.4 formats support backplane clocks                                                                                                                            |                                                     |     |

| е | Select which clock reference source to use                                                                                                                                      | SetClockSource<br>SetExternalReferenceFre<br>quency | 5.5 |

| f | The internal clock generator for the sampling clock                                                                                                                             |                                                     | 5.6 |

| g | Select which sampling clock source to use; internal or direct external sampling clock.                                                                                          | SetClockSource                                      | 5.7 |

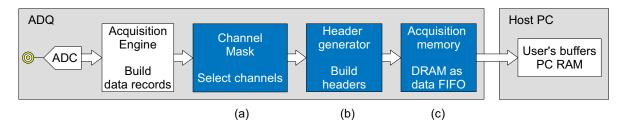

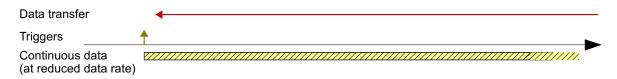

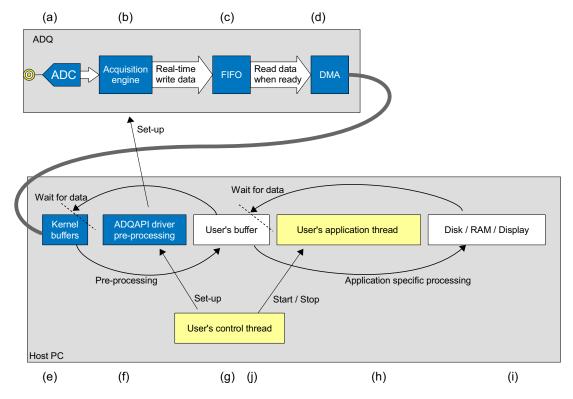

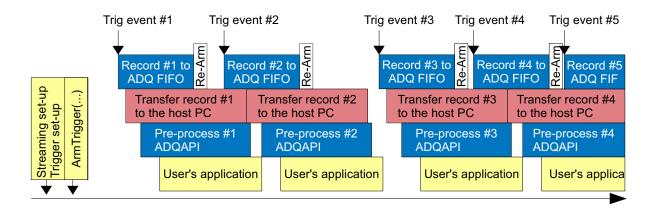

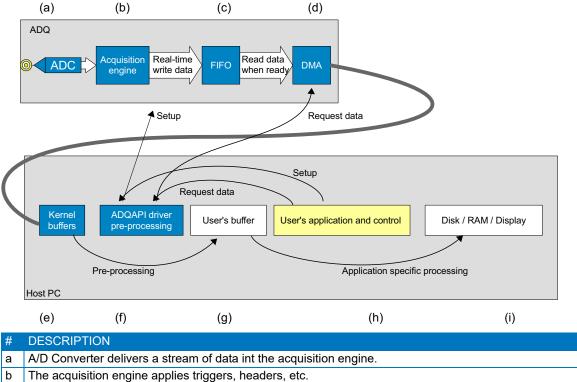

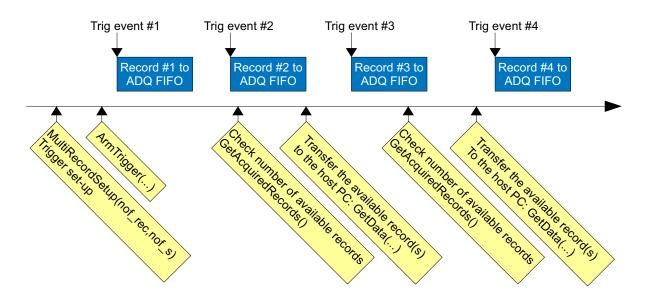

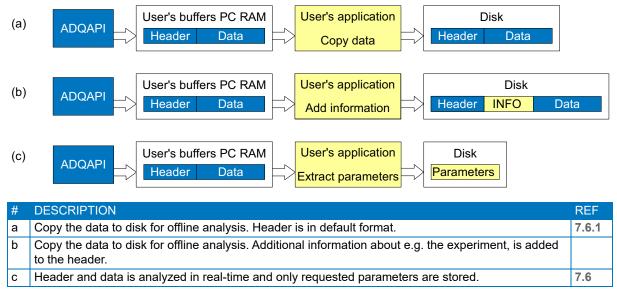

| h | Reduce sample rate with sample skip.                                                                                                                                            | SetSampleSkip                                       | 5.9 |