# ADQ33-PDRX Datasheet

The ADQ33-PDRX is a high-speed digitizer with extended dynamic range for pulse data applications. The ADQ33-PDRX features:

- One analog input channel

- 12 bits resolution

- 3 bits dynamic range extension through built-in dual-gain channel combination

- 1 GSPS sampling rate

- 7 GByte/s sustained data transfer rate to GPU

- 7 GByte/s sustained data transfer rate to CPU

- Two external triggers

- General Purpose Input/Output (GPIO)

- Open FPGA for real-time signal processing

- Firmware option for averaging of records

- Firmware option for pulse analysis

#### **1** ORDERING INFORMATION

ADQ33-PDRX is available with a set of options. Follow the procedure to configure the ADQ33. Start with the hardware configurations. These are factory installed and cannot be changed through software commands.

- 1. Dual-gain channel-combination analog front-end **-PDRX** is included on ADQ33-PDRX. For standard DCcoupled analog front-end, see 20-2451 ADQ33 datasheet.

- 2. PCIe interface is standard.

Select the firmware options. The firmware FWDAQ is always included. Additional firmware files are distributed as files and can be loaded into the board at any time.

- 3. Data acquisition firmware -FWDAQ is always included

- 4. Select one or several of available firmware packages, -FWATD, -FWPD.

- 5. On-board channel combination for dual-gain pulse detection is included on ADQ33-PDRX for all firmware options.

- 6. Select accessories, open FPGA development kit **DEVDAQ**, **DEVPD**<sup>1</sup>.

- 7. Select extended warranty -W5Y.

The open FPGA is accessed through the design project for each firmware. For **-FWDAQ**, the development kit is **DEVDAQ**. For **-FWPD**, the development kit is **DEVPD**. The **DEVDAQ** is a one-time purchase. The FPGA bit files built from the design project can be used on any ADQ33 with a valid FWDAQ license (included on all units).

<sup>&</sup>lt;sup>1</sup> DEVPD is available in 2024. Contact Teledyne SP Devices for more information.

#### 2 ADQ33-PDRX INTRODUCTION

#### 2.1 Features

- One input channel

- 1 GSPS sampling rate

- 12 bits resolution

- 3 bits dynamic range extension through built-in dual gain channel combination

- DC-coupled with 760 MHz bandwidth

- Programmable DC offset

- Internal and external clock reference

- Internal and external sampling clock

- Clock reference output

- Internal and external triggers

- 8 Gbytes data memory

- 7 Gbyte/s sustained data streaming to CPU and GPU

- Data interface PCIe Gen3 x8

- Averaging firmware FWATD

- Pulse analysis firmware FWPD

#### 2.2 Applications

- Time-of-flight mass spectrometry

- LIDAR

- Pulse data systems

#### 2.3 Advantages

- ADQ33-PDRX integrates the analog dual-gain amplifier for a compact high-performance system solution

- Real-time processing for pulse data capture and high data throughput

- Teledyne SP Devices' design services are available for fast integration to reduce time-tomarket

#### 2.4 System design optimization; open FPGA and streaming to CPU and GPU

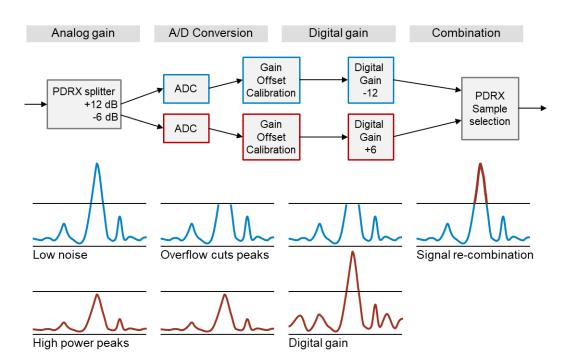

High-performance data acquisition systems require high speed real-time analysis. ADQ33-PDRX uses a built-in dual-gain channel combination to increase the dynamic range in pulse capture. Weak pulses are captured through a channel with high gain and strong pulses are captured through a channel with low gain. The channel combination results in a dynamic range extension equivalent to 3 extra bits of vertical resolution.

The PDRX channel combination is carried out by the digitizer firmware and is available for **FWATD**, **FWPD** and **FWDAQ**.

#### Figure 1 Principle of channel combination

The ADQ33-PDRX hardware can also be used for custom channel combination. The combination firmware is then bypassed, and the board operate with 2 channels output.

In addition to the specific pulse detection, ADQ33-PDRX supports a variety of options for efficient system design:

# Streaming to GPU

ADQ33-PDRX supports up to 7 GByte/s peer-to-peer streaming and streaming via pinned buffer to GPU. A GPU offers a powerful platform for implementing application-specific signal processing algorithms.

# Streaming to CPU

ADQ33-PDRX supports up to 7 GByte/s to host computer. Implementing the application-specific algorithms in the CPU results in an efficient system.

# **Open FPGA for real-time processing**

ADQ33-PDRX offers an open FPGA for implementation of the application-specific computations in the FPGA. This gives the most compact system design. Firmware development kit is ordered separately.

#### **3 TECHNICAL DATA**

Technical parameters are valid for ADQ33-PDRX operating with firmware FWDAQ. All parameters are typical unless otherwise noted.

# Table 1 Analog input (front panel label A)

| Parameter                       | Condition | Min  | Typical | Max  | Unit      |

|---------------------------------|-----------|------|---------|------|-----------|

| Basic parameters                |           |      |         |      |           |

| Number of channels              |           |      | 1       |      |           |

| Sampling rate                   |           |      | 1       | 1    | Gsample/s |

| Bandwidth                       | -3dB      |      | 660     |      | MHz       |

| Input range                     |           |      | 1       |      | Vpp       |

| Input impedance                 |           |      | 50      |      | Ω         |

| Coupling                        |           |      | DC      |      |           |

| Connector type                  |           |      | SMA     |      |           |

| Programmable DC-offset          |           |      |         |      | 1         |

| DC-offset range                 |           | -0.5 |         | +0.5 | V         |

| Dynamic performance             |           |      |         |      |           |

| Idle channel noise <sup>2</sup> |           |      | 71      |      | dBFS      |

| ENOB noise based <sup>3</sup>   |           |      | 11.5    |      | bits      |

#### Table 2 Comparison of ADQ33-PDRX to ADQ33

| Parameter                  | Condition        | ADQ33         | ADQ33-PDRX  | Unit |

|----------------------------|------------------|---------------|-------------|------|

| RMS noise                  | Terminated input | 250           | 100         | μV   |

| Max input range            |                  | 0.5           | 1           | Vpp  |

| DC-offset                  |                  | -0.25 to 0.25 | -0.5 to 0.5 | V    |

| Dynamic range <sup>4</sup> |                  | 57            | 71          | dB   |

| ENOB⁵                      |                  | 9.2           | 11.5        | bits |

| Bandwidth                  | -3dBFS           | 1000          | 660         | MHz  |

| Attenuation at 1GHz        |                  | 3             | 5.1         | dB   |

<sup>&</sup>lt;sup>2</sup> Measured integrated noise with a terminated input. Noise level is computed relative a full-scale sine wave.

<sup>&</sup>lt;sup>3</sup> Computed from idle channel noise. See figure for ENOB at sweep of input power.

<sup>&</sup>lt;sup>4</sup> Power of full-scale sine wave relative noise with terminated input.

<sup>&</sup>lt;sup>5</sup> Computed from "Dynamic Range" in

Table 2 using the formula (Dynamic Range -1.76) / 6.02.

# Table 3 Clock generator and front panel CLK connector.

| Parameter                            | Condition            | Min                  | Typical                | Max     | Unit |

|--------------------------------------|----------------------|----------------------|------------------------|---------|------|

| Connector type                       |                      |                      | SMA                    |         |      |

| Internal clock reference             |                      |                      |                        |         |      |

| Frequency                            |                      |                      | 10                     |         | MHz  |

| Accuracy                             |                      |                      | ±3                     |         | ppm  |

|                                      |                      |                      | ±1/year                |         |      |

| Internal sampling clock gen          | erator               |                      |                        |         |      |

| Frequency                            |                      |                      | 1000                   |         | MHz  |

| External clock reference inp         | ut (from front panel | <b>CLK connect</b>   | or) <sup>6</sup>       |         |      |

| Frequency                            |                      | 1                    | 10                     | 500     | MHz  |

| Frequency <sup>7</sup>               | Jitter cleaner       | 10                   | 10                     | 500     | MHz  |

|                                      | enabled              | -10 ppm              |                        | +10 ppm |      |

| Frequency                            | Delay line used      |                      | 10                     | 100     | MHz  |

| Delay line tuning range <sup>8</sup> |                      |                      | 500                    |         | ps   |

| Signal level                         |                      | 0.5                  |                        | 3.3     | Vpp  |

| Input impedance                      | AC                   |                      | 50                     |         | Ω    |

| Input impedance                      | DC                   |                      | 10k                    |         | Ω    |

| Input impedance (high) <sup>9</sup>  | AC                   |                      | 200                    |         | Ω    |

| Clock reference output (on           | front panel CLK conr | ector) <sup>10</sup> |                        |         |      |

| Frequency                            |                      |                      | 10                     |         | MHz  |

| Signal level                         | Into 50-Ω load       |                      | 1.2                    |         | Vpp  |

| Output impedance                     | AC                   |                      | 50                     |         | Ω    |

| Output impedance                     | DC                   |                      | 10k                    |         | Ω    |

| External direct sampling clo         | ck input (from front | panel CLK co         | nnector) <sup>11</sup> |         |      |

| Frequency <sup>12</sup>              |                      |                      | 1000                   |         | MHz  |

| Signal level                         |                      | 0.5                  |                        | 3.3     | Vpp  |

| Impedance                            | AC                   |                      | 50                     |         | Ω    |

| Impedance                            | DC                   |                      | 10k                    |         | Ω    |

<sup>9</sup> Software-selectable high-impedance mode.

<sup>&</sup>lt;sup>6</sup> Using a clock reference from an external source to synchronize the ADQ33 to the external source.

$<sup>^7</sup>$  The jitter cleaner requires the reference frequency to be a multiple of 10 MHz within  $\pm$  10ppm.

<sup>&</sup>lt;sup>8</sup> Tuning of sampling clock phase relative to external clock reference input phase.

<sup>&</sup>lt;sup>10</sup> The internal clock reference of the ADQ33-PDRX is made available to synchronize external equipment.

<sup>&</sup>lt;sup>11</sup> Using an external clock while bypassing the internal clock generator.

<sup>&</sup>lt;sup>12</sup> In single-channel mode, the sampling frequency is 2 times the external clock frequency.

#### Table 4 Front panel TRIG connector

| Parameter                      | Condition      | Min  | Typical | Max  | Unit |

|--------------------------------|----------------|------|---------|------|------|

| Connector type                 |                | SMA  |         |      |      |

| Used as input (or GPIO)        | ·              |      |         |      |      |

| Impedance                      | DC             |      | 50      |      | Ω    |

| Impedance (high) <sup>13</sup> | DC             |      | 500     |      | Ω    |

| Signal level                   | 50-Ω mode      | -0.5 |         | 3.3  | V    |

| Adjustable threshold           | 50-Ω mode      | 0    |         | 2.8  | V    |

| Signal level                   | High impedance | -0.5 |         | 5.5  | V    |

| Adjustable threshold           | High impedance | 0    |         | 2.3  | V    |

| Pulse repetition frequency     | As trigger     |      |         | 10   | MHz  |

| Time resolution <sup>14</sup>  | As trigger     |      | 125     |      | ps   |

| Update rate <sup>14</sup>      | As GPIO        |      |         | 62.5 | MHz  |

| Used as output (or GPIO)       |                |      |         |      |      |

| Impedance                      | DC             |      | 50      |      | Ω    |

| Output level high VOH          | Into 50-Ω load | 1.8  |         |      | V    |

| Output level low VOL           | Into 50-Ω load |      |         | 0.1  | V    |

| Pulse repetition frequency     |                |      |         | 62.5 | MHz  |

# Table 5 Front panel SYNC connector (may be used as a trigger source with larger timing grid)

| Parameter                      | Condition      | Min  | Typical | Max  | Unit |

|--------------------------------|----------------|------|---------|------|------|

| Connector type                 |                |      | SMA     |      |      |

| Used as input (or GPIO)        |                |      |         |      | ·    |

| Impedance                      | DC             |      | 50      |      | Ω    |

| Impedance (high) <sup>13</sup> | DC             |      | 500     |      | Ω    |

| Signal range                   | 50-Ω mode      | -0.5 |         | 3.3  | V    |

| Adjustable threshold           | 50-Ω mode      | 0    |         | 2.8  | V    |

| Signal level                   | High impedance | -0.5 |         | 5.5  | V    |

| Adjustable threshold           | High impedance | 0    |         | 2.3  | V    |

| Pulse repetition frequency     | As trigger     |      |         | 10   | MHz  |

| Time resolution <sup>14</sup>  | As trigger     |      | 8       |      | ns   |

| Update rate <sup>14</sup>      | As GPIO        |      |         | 62.5 | MHz  |

| Used as output (or GPIO)       |                |      |         |      | ·    |

| Impedance                      | DC             |      | 50      |      | Ω    |

| Output level high VOH          | Into 50-Ω load | 1.8  |         |      | V    |

| Output level low VOL           | Into 50-Ω load |      |         | 0.1  | V    |

| Pulse repetition frequency     |                |      |         | 62.5 | MHz  |

<sup>&</sup>lt;sup>13</sup> Software-selectable high-impedance mode.

<sup>&</sup>lt;sup>14</sup> Timing properties are valid for 2.5 GSPS in 2 channel mode and 5 GSPS in 1 channel mode. Timing properties scale linearly with sampling frequency.

#### **Table 6 Front panel GPIO connector**

| Parameter                      | Condition      | Min | Typical | Max  | Unit |

|--------------------------------|----------------|-----|---------|------|------|

| Connector type                 |                |     | SMA     |      |      |

| Used as input                  | · · · ·        |     |         |      |      |

| Impedance                      |                |     | 50      |      | Ω    |

| Impedance (high) <sup>13</sup> |                |     | 10      |      | kΩ   |

| Input level high VIH           |                | 2   |         |      | V    |

| Input level low VIL            |                |     |         | 0.8  | V    |

| Update rate <sup>14</sup>      |                |     |         | 62.5 | MHz  |

| Used as output                 |                |     | - I     |      |      |

| Output Impedance               |                |     | 50      |      | Ω    |

| Output level high VOH          | Into 50-Ω load | 1.5 |         |      | V    |

| Output level high VOH          | No load        | 3.2 |         |      | V    |

| Output level low VOL           | Into 50-Ω load |     |         | 0.1  | V    |

| Output level low VOL           | No load        |     |         | 0.1  | V    |

| Update rate <sup>14</sup>      |                |     |         | 62.5 | MHz  |

# Table 7 Custom GPIO expansion. See section 10.

| Parameter                              | Value                                  |

|----------------------------------------|----------------------------------------|

| Connector type                         | 40-pin FFC/FPC connector, pitch 0.5 mm |

| Number of differential IO signals LVDS | 8                                      |

| Number of single-ended IO signals 3.3V | 5                                      |

# **Table 8 Environment and mechanical parameters**

| Parameter                       | Condition                                                    | Min  | Typical | Max        | Unit |

|---------------------------------|--------------------------------------------------------------|------|---------|------------|------|

| Power and temperature           |                                                              |      |         |            |      |

| Power consumption <sup>15</sup> | FWDAQ                                                        |      | 30      |            | W    |

| Power supply                    |                                                              | 10.8 | 12      | 13.2       | V    |

| Operating temperature           | At fan inlet                                                 | 0    |         | 45         | °C   |

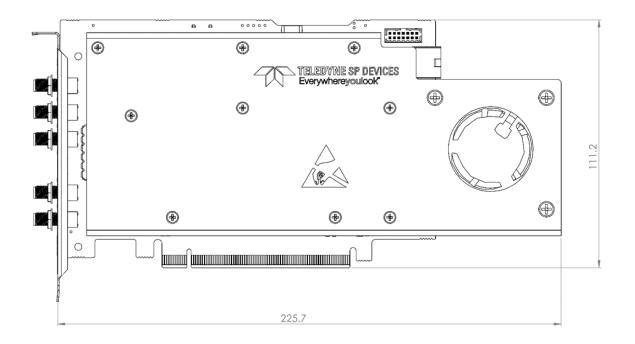

| Size                            |                                                              |      |         |            |      |

| Width                           |                                                              |      | 1       |            | slot |

| Length                          |                                                              |      | 225.7   |            | mm   |

| Height                          |                                                              |      | 111.2   |            | mm   |

| Compliances                     |                                                              |      |         |            |      |

| RoHS3                           |                                                              | Yes  |         |            |      |

| CE                              |                                                              | Yes  |         |            |      |

| FCC                             | Exclusion according to CFR 47, part 15, paragraph 15.103(c). |      |         | L5.103(c). |      |

<sup>&</sup>lt;sup>15</sup> Power consumption depends on firmware option and use case. Power consumption is measured during acquisition and streaming of data at 4 Gbyte/s to PC.

#### Table 9 Data acquisition

| Parameter                   | Condition                     | Min | Typical | Max                | Unit    |

|-----------------------------|-------------------------------|-----|---------|--------------------|---------|

| Rearm time <sup>16</sup>    |                               |     |         | 20                 | ns      |

| Acquisition memory          | Shared by all channels        |     | 8       |                    | Gbyte   |

| (Data FIFO)                 |                               |     |         |                    |         |

| Record length               | 2 channels mode               | 16  |         | 2 <sup>32</sup> -1 | samples |

|                             | Combined channels             | 16  |         | 2 <sup>32</sup> -1 | samples |

| Pretrigger <sup>17</sup>    | 2 channels mode in steps of 8 | 8   |         | 16 360             | samples |

|                             | Combined in steps of 8        | 8   |         | 16 360             | samples |

| Trigger delay <sup>18</sup> | 2 channels mode in steps of 8 | 8   |         | 2 <sup>35</sup> -8 | samples |

|                             | Combined in steps of 8        | 8   |         | 2 <sup>35</sup> -8 | samples |

## Table 10 Data transfer

| Parameter                                               | Value              | Unit    |

|---------------------------------------------------------|--------------------|---------|

| Supported versions of data transfer standard PCIe       | Gen1 / Gen2 / Gen3 |         |

| Supported number of lanes <sup>19</sup>                 | 1/4/8              |         |

| Data rate to CPU sustained with headers                 | 5                  | GByte/s |

| Data rate to CPU sustained without headers              | 7                  | GByte/s |

| Data rate to GPU sustained without headers              | 7                  | GByte/s |

| Data rate peer-to-peer to GPU sustained without headers | 7                  | GByte/s |

# Table 11 Software support

| Parameter                      | Value            |

|--------------------------------|------------------|

| Operating system <sup>20</sup> | Windows / Linux  |

| GUI                            | Digitizer Studio |

| Example code                   | C, Python        |

| API                            | C / C++          |

<sup>&</sup>lt;sup>16</sup> Minimum time from the last sample of a record to the next trigger.

<sup>&</sup>lt;sup>17</sup> Pre-trigger is set by assigning the parameter "horizontal offset" a negative value

<sup>&</sup>lt;sup>18</sup> Trigger delay is set by assigning the parameter "horizontal offset" a positive value

<sup>&</sup>lt;sup>19</sup> The ADQ30 must be installed in a 16 lanes slot or a slot with a connector with an open end.

<sup>&</sup>lt;sup>20</sup> See 15-1494 Operating system support for a detailed listing of supported distributions.

# 4 FEATURES FOR DATA FLOW CONTROL, SYNCHRONIZATION AND PROCESSING

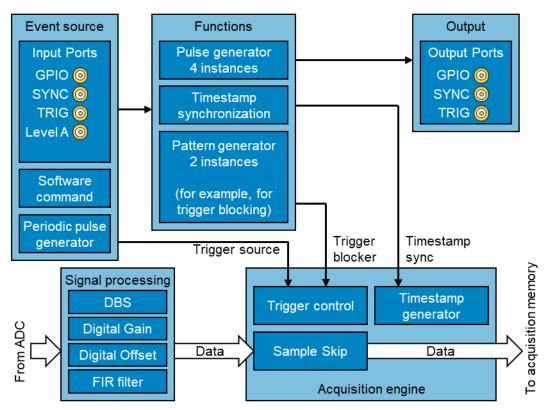

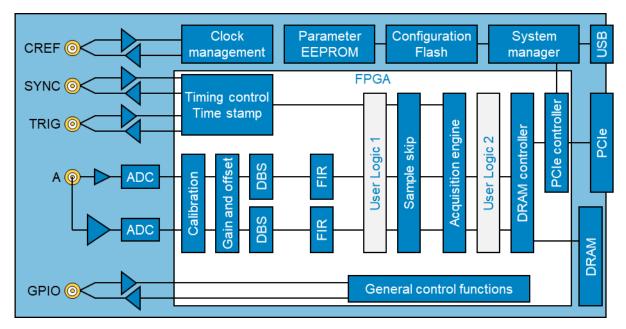

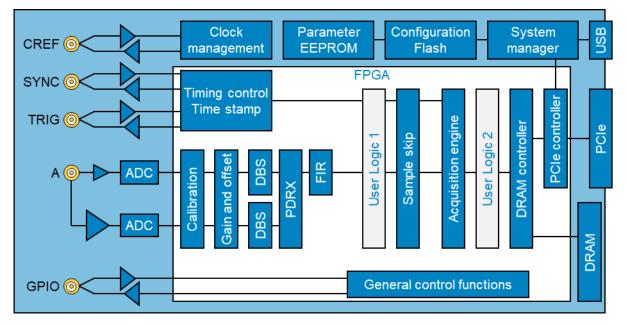

The ADQ33-PDRX features an advanced machine for flow control, synchronization, and signal processing. The block diagrams are shown in Figure 2 and Figure 3. The features are described in the following tables.

Figure 2 Flow control and synchronization block diagram.

#### Table 12 Digital signal processing blocks

| Object type                            | Available selections              |

|----------------------------------------|-----------------------------------|

| Digital Signal Processing              | Digital Baseline Stabilizer (DBS) |

| Included signal processing in the data | Digital gain                      |

| path for enhanced signal quality.      | Digital offset                    |

|                                        | Digital FIR filter                |

### **Table 13 Flow control blocks**

| Object type                                 | Available selections                                  |

|---------------------------------------------|-------------------------------------------------------|

| Input ports                                 | Front panel TRIG                                      |

| Electrical connections to the ADQ33 for     | Front panel SYNC                                      |

| real-time operation (excluding the PCIe     | Front panel GPIO                                      |

| data interface) Used as event source.       | Front panel CLK (clock reference or clock input only) |

|                                             | Analog channel A                                      |

| Event sources                               | Software command                                      |

| Signals for real-time control of activities | External TRIG                                         |

| in the firmware of ADQ33.                   | External SYNC                                         |

|                                             | External GPIO                                         |

|                                             | Internal periodic event generator                     |

|                                             | Level analog channel                                  |

| Functions                                   | Pattern generator for timestamp synchronization       |

| Included operations for real-time control   | Pattern generator general purpose, 2 instances        |

| of activities in the firmware of ADQ33.     | Pulse generator, 4 instances                          |

| Output ports                                | Front panel TRIG                                      |

| Electrical connections to the ADQ33 for     | Front panel SYNC                                      |

| real-time operation (excluding the PCIe     | Front panel GPIO                                      |

| data interface).                            | Front panel CLK (clock reference output only)         |

#### Table 14 Firmware functions for flow control

| Function              | Modes/selections | Event sources as stimuli          |

|-----------------------|------------------|-----------------------------------|

| Pattern generator for |                  | Software command                  |

| timestamp             |                  | External TRIG                     |

| synchronization       |                  | External SYNC                     |

| Control the time of   |                  | Internal periodic event generator |

| the ADQ33-PDRX.       |                  |                                   |

| Pulse generator       | Rising edge      | Software command                  |

| Control output pulse  | Falling edge     | External TRIG                     |

| shapes. Three         | Pulse length     | External SYNC                     |

| instances.            | Polarity         | Internal periodic event generator |

| Pattern generator     | Once             | Software command                  |

| general purpose       | Window           | External TRIG                     |

| For example, used for | Gate             | External SYNC                     |

| trigger blocking.     | Trigger counter  | Internal periodic event generator |

# Table 15 Firmware functions for acquisition

| Function                 | Modes                       | Event Sources as stimuli / control |

|--------------------------|-----------------------------|------------------------------------|

| Trigger                  |                             | Software command                   |

| Initiate the acquisition |                             | External TRIG                      |

| of a data record.        |                             | External SYNC                      |

|                          |                             | Internal periodic event generator  |

|                          |                             | Level analog channel A             |

| Data acquisition         | Fixed record length         | Selected Trigger                   |

| modes                    | Dynamic record length (zero |                                    |

| Configurations for       | suppression)                |                                    |

| sending digital data to  |                             |                                    |

| the host PC.             |                             |                                    |

| Data transfer modes      | Streaming with header       | User set-up                        |

| Transport to CPU /       | Streaming without header    |                                    |

| GPU                      |                             |                                    |

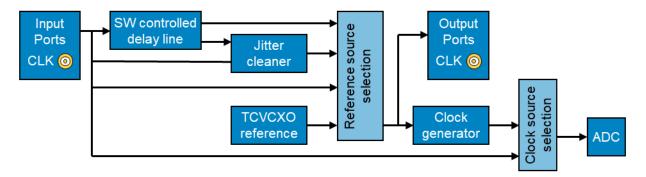

# Figure 3 Clock generation block diagram.

#### **Table 16 Clock generation**

| Function                                   | Modes                                          |

|--------------------------------------------|------------------------------------------------|

| Clock reference source                     | Internal                                       |

| Phase and frequency reference for the      | External                                       |

| clock system.                              | External with jitter cleaner and/or delay line |

| Sampling clock sources                     | Internal clock generator                       |

| Actual clock for taking the samples of the | Direct external clock                          |

| analog data.                               |                                                |

| Clock output                               | Selected clock reference                       |

# 5 FIRMWARE

#### 5.1 FWDAQ

The FWDAQ is included with all digitizers. The firmware includes control of the hardware and recording of data.

The channel combination is included in FWDAQ for ADQ33-PDRX hardware.

#### 5.2 FWATD

The FWATD is optional. It includes thresholding for noise suppression and accumulations of waveforms. See datasheet 22-2912 for more details.

The channel combination is included in FWATD for ADQ33-PDRX hardware.

#### 5.3 FWPD

The FWPD is optional. It includes detection and analysis of pulses. See datasheet 23-3028 for more details.

The channel combination is included in FWPD for ADQ33-PDRX hardware.

#### 5.4 Managing firmware

The digitizer supports multiple firmware images. Note the following about managing firmware images:

- The non-volatile memory on the digitizer can store up to four different firmware images (including the active firmware). Use the tool ADQAssist to change firmware and to upload new images to the digitizer.

- Each hardware can include a license for multiple firmware options. If all firmware images cannot be stored on the device, some may need be stored on the host computer for manual reprogramming via ADQAssist.

- The digitizer (and the enclosing host computer) must be power cycled for the firmware switch to be completed. This is required to let the PCIe bus enumerate with the new firmware.

- Some firmware features require a valid license key to activate. See the ordering information section for details about available firmware features.

#### 6 ABSLOUTE MAXIMUM RATINGS

#### **Table 17 Absolute maximum ratings**

| Parameter                            | Condition                 | Min  | Max | Unit |

|--------------------------------------|---------------------------|------|-----|------|

| Power supply to GND                  |                           | -0.4 | 14  | V    |

| Operating temperature                |                           | 0    | 45  | °C   |

| Analog in to GND Peak                |                           | -7   | +7  | V    |

| Analog in to GND DC                  |                           | -3   | +3  | V    |

| TRIG to GND                          | 50-Ω mode                 | -2   | 5   | V    |

| SYNC to GND                          | 50-Ω mode                 | -2   | 5   | V    |

| TRIG to GND                          | 500-Ω mode                | -2   | 6   | V    |

| SYNC to GND                          | 500-Ω mode                | -2   | 6   | V    |

| CLK REF to GND AC amplitude          |                           |      | 5   | Vpp  |

| CLK REF to GND DC-level              |                           | -5   | 5   | V    |

| GPIO to GND                          |                           | -1.5 | 5   | V    |

| FFC / FPC differential signal to GND | Powered <sup>21</sup>     | -0.5 | 2.3 | V    |

|                                      | Not powered <sup>21</sup> | -0.5 | 0.5 | V    |

| FFC / FPC single-ended signal to GND | Powered <sup>21</sup>     | -0.3 | 3.8 | V    |

| 21                                   | Not powered <sup>21</sup> | -0.3 | 0.5 | V    |

Exposure to conditions exceeding these ratings may reduce lifetime or permanently damage the digitizer. The digitizer with PCIe format has a built-in fan to cool the device. The built-in temperature monitoring unit will protect the digitizer from overheating by temporarily shutting down parts of the device in an overheat situation.

The SMA connectors have an expected lifetime of 500 operations. For frequent connecting and disconnecting of cables, connector savers are recommended.

<sup>&</sup>lt;sup>21</sup> The absolute maximum ratings depend on whether the ADQ33-PDRX is powered or not. It is recommended to use the respective power rail in the FFC connector to power or enable the external drivers to avoid driving overvoltage into an unpowered digitizer. Use the 1.8 V rail for the differential signals and 3.3 V for the single-ended signals.

#### 7 TYPICAL PERFORMANCE

#### 7.1 Frequency response

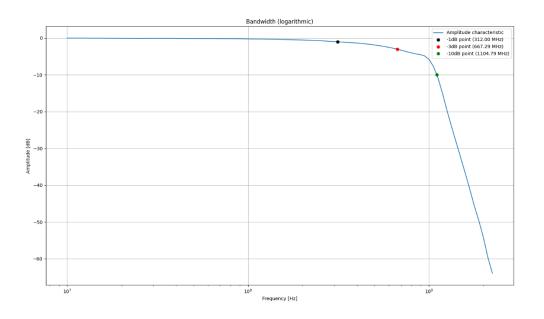

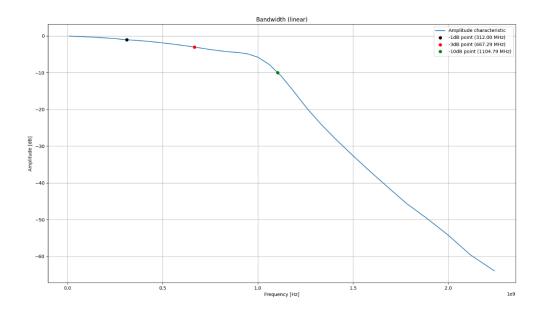

#### Figure 4 Frequency response logarithmic frequency scale, typical performance.

Figure 5 Frequency response linear frequency scale, typical performance.

#### 8 BLOCK DIAGRAM

Figure 6 Block diagram ADQ33-PDRX-FWDAQ-PCIe bypass channel combination

# Figure 7 Block diagram ADQ33-PDRX-FWDAC-PCIe

Figure 6 shows a block diagram of ADQ33-PDRX using FWDAQ when the channel combination is bypassed. The two signals with different gain are passed to the user for channel combination.

Figure 7 shows a block diagram of ADQ33-PDRX using FWDAQ including channel combination. There is only one output channel.

The boxes "User Logic" are open for custom real-signal processing thought the firmware development kit (purchased separately).

#### 9 HOST PC INTERFACE PCIE

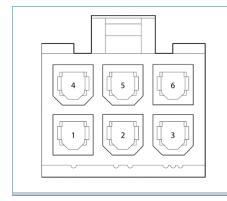

The ADQ33-PDRX-PCIe is powered from the power supply of the PC via a PCI Express 6-pin (2x3) auxiliary power supply connector. The connection in the cable should be as in Figure 8. A suitable connector is for example Molex 45559-0002.

It is important that the auxiliary power supply is turned on immediately when the PC starts. Otherwise, the digitizer will not be recognized on the PCI Express bus.

| <br>Pin | Signal         |

|---------|----------------|

| 1       | +12 V          |

| 2       | +12 V          |

| 3       | +12 V          |

| 4       | Ground         |

| 5       | Sense (Ground) |

| 6       | Ground         |

Figure 8 Power supply connection. Cable connector, looking into the connector end.

#### **10 GPIO EXPANSION**

The FFC connector allows direct access to the FPGA for building custom expansion boards. The FFC connector requires custom firmware and is accessible through the FPGA development kit. The ADQ33-PDRX user guide document number 21-2539 contains a description of connector.

Note that this connector is connected directly to the FPGA. Damage caused by custom hardware failure is not covered by warranty.

Contact Teledyne SP Devices' sales representative for more information.

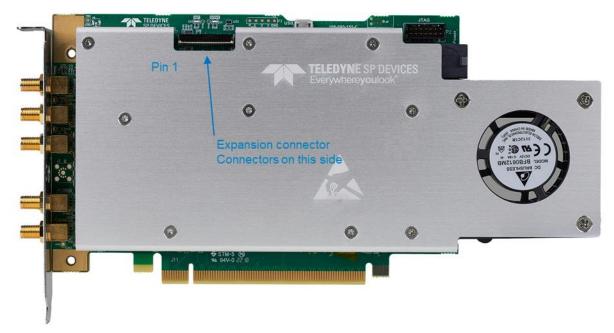

Figure 9 ADQ33-PDRX photo showing GPIO expansion connection on the top side.

#### 11 MECHANICAL DRAWING

#### **Figure 10 Mechanical drawing**

#### 12 REFERENCES

Refer to TSPD's web site spdevices.com for the latest version of documents.

15-1494 Supported operating systems

18-2059 ADQUpdater user guide

20-2451 ADQ33 datasheet

20-2507 ADQ3 series development kit user guide

20-2521 ADQAssist user guide

21-2539 ADQ3 series user guide

- 22-2912 ADQ3 FWATD datasheet

- 23-3028 ADQ3 FWPD datasheet

#### **Important Information**

Teledyne Signal Processing Devices Sweden AB (Teledyne SP Devices) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to Teledyne SP Devices' general terms and conditions supplied at the time of order acknowledgment. Teledyne SP Devices warrants that each product will be free of defects in materials and workmanship, and conform to specifications set forth in published data sheets, for a period of three (3) years. The warranty commences on the date the product is shipped by Teledyne SP Devices. Teledyne SP Devices' sole liability and responsibility under this warranty is to repair or replace any product which is returned to it by Buyer and which Teledyne SP Devices determines does not conform to the warranty. Product returned to Teledyne SP Devices for warranty service will be shipped to Teledyne SP Devices at Buyer's expense and will be returned to Buyer at Teledyne SP Devices' expense. Teledyne SP Devices will have no obligation under this warranty for any products which (i) has been improperly installed; (ii) has been used other than as recommended in Teledyne SP Devices' installation or operation instructions or specifications; or (iii) has been repaired, altered or modified by entities other than Teledyne SP Devices. The warranty of replacement products shall terminate with the warranty of the product. Buyer shall not return any products for any reason without the prior written authorization of Teledyne SP Devices.

In no event shall Teledyne SP Devices be liable for any damages arising out of or related to this document or the information contained in it.

TELEDYNE SP DEVICES' EXPRESS WARRANTY TO BUYER CONSTITUTES TELEDYNE SP DEVICES' SOLE LIABILITY AND THE BUYER'S SOLE REMEDY WITH RESPECT TO THE PRODUCTS AND IS IN LIEU OF ALL OTHER WARRANTIES, LIABILITIES AND REMEDIES. EXCEPT AS THUS PROVIDED, TELEDYNE SP DEVICES DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING ANY WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT.

TELEDYNE SP DEVICES DOES NOT INDEMNIFY, NOR HOLD THE BUYER HARMLESS, AGAINST ANY LIABILITIES, LOSSES, DAMAGES AND EXPENSES (INCLUDING ATTORNEY'S FEES) RELATING TO ANY CLAIMS WHATSOEVER. IN NO EVENT SHALL TELEDYNE SP DEVICES BE LIABLE FOR SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES, INCLUDING LOST PROFIT, LOST DATA AND THE LIKE, DUE TO ANY CAUSE WHATSOEVER. NO SUIT OR ACTION SHALL BE BROUGHT AGAINST TELEDYNE SP DEVICES MORE THAN ONE YEAR AFTER THE RELATED CAUSE OF ACTION HAS ACCRUED. IN NO EVENT SHALL THE ACCRUED TOTAL LIABILITY OF TELEDYNE SP DEVICES FROM ANY LAWSUIT, CLAIM, WARRANTY OR INDEMNITY EXCEED THE AGGREGATE SUM PAID TO SP BY BUYER UNDER THE ORDER THAT GIVES RISE TO SUCH LAWSUIT, CLAIM, WARRANTY OR INDEMNITY.

# Worldwide Sales and Technical Support

www.spdevices.com

# **Teledyne SP Devices Corporate Headquarters**

Teknikringen 8D SE-583 30 Linköping Sweden Phone: +46 (0)13 465 0600 Fax: +46 (0)13 991 3044 Email: <u>info@spdevices.com</u>

Copyright © 2024 Teledyne Signal Processing Devices Sweden AB. All rights reserved, including those to reproduce this publication or parts thereof in any form without permission in writing from Teledyne SP Devices.